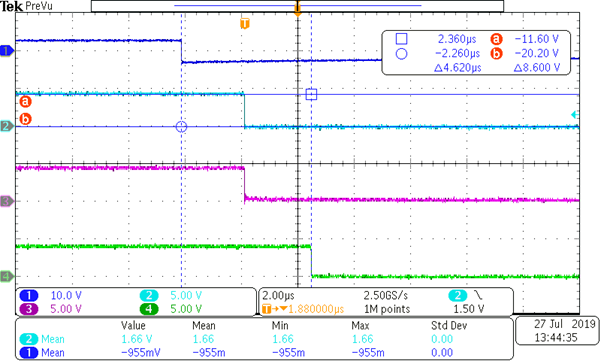

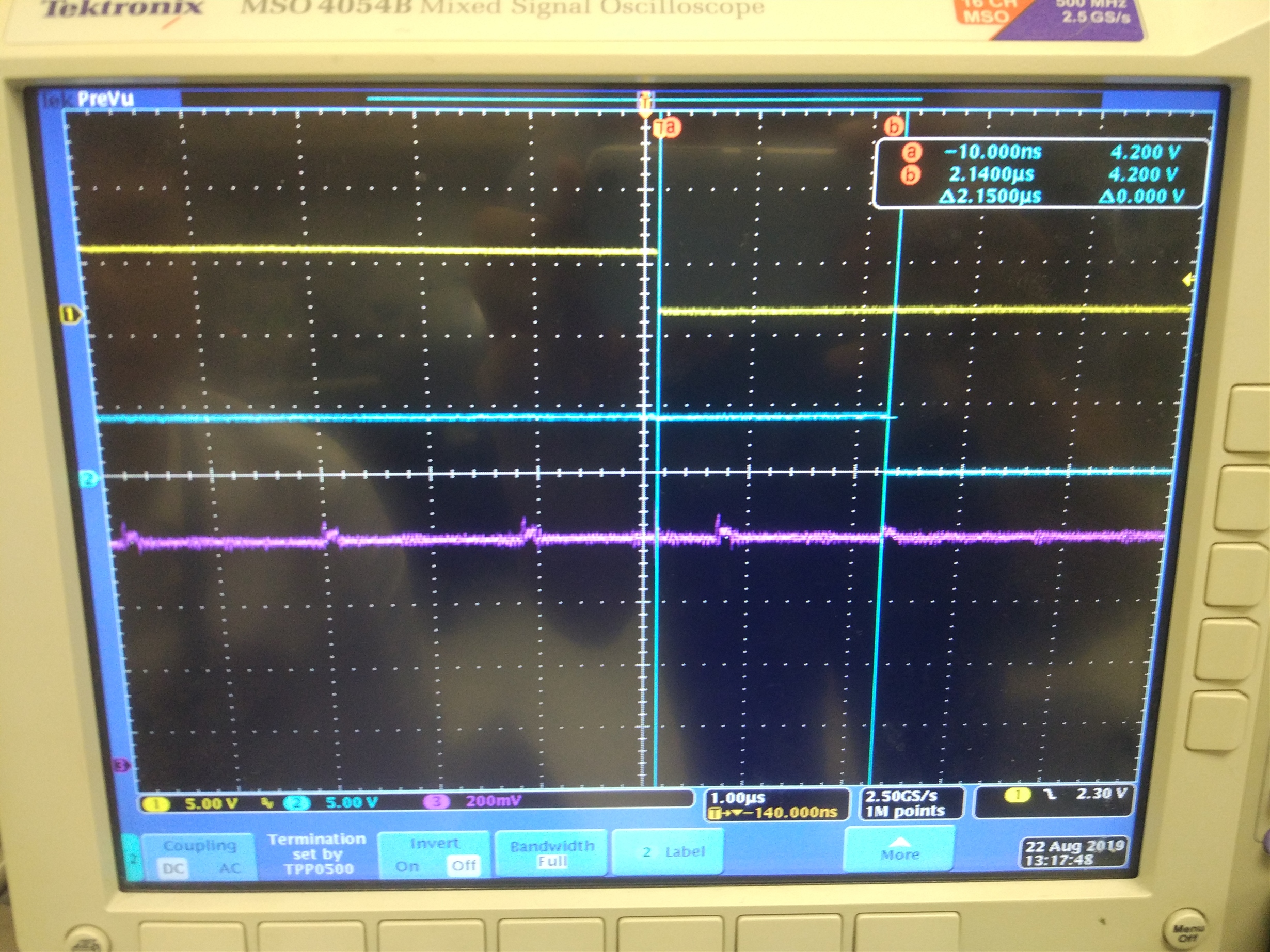

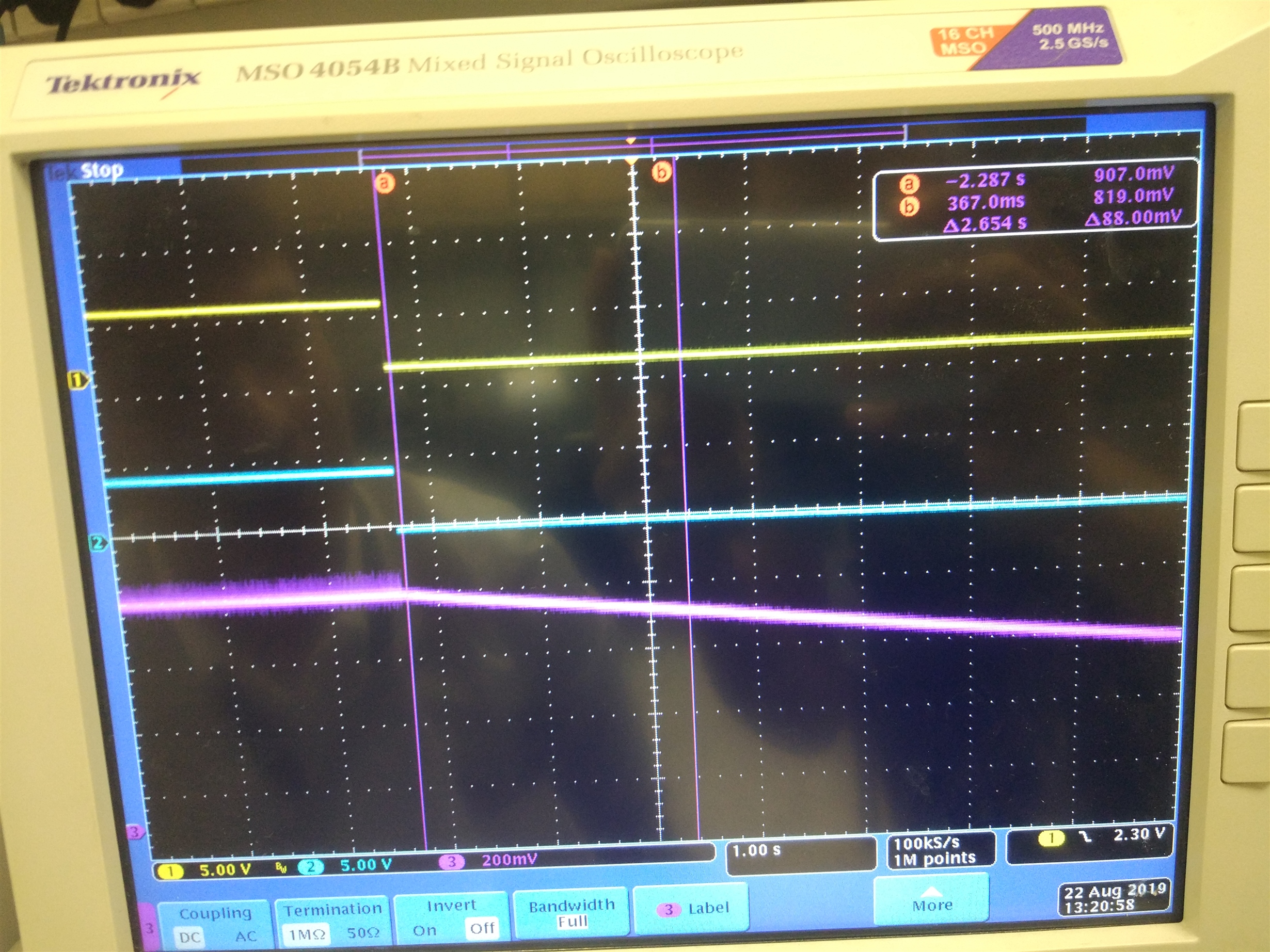

这是我在 TPS543C20EVM 上的断电序列测试。 1通道为模块 A 的 EN、2通道为模块 A 的 PGD、3通道为模块 B 的 EN、4通道为模块 B 的 PGD 当模块 A 的 EN 变为低电平时、PGD 也会在延迟后变为低电平。 接下来、模块 B 的 EN 变为低电平、PGD 也在延迟后变为低电平。 模块 A 的 EN 禁用与模块 B 的 PGD 响应之间的时间为4.62us。 但是、在数据表中、PGOOD 的输出延迟为2us。

测试条件:12V 输入电压、空载。

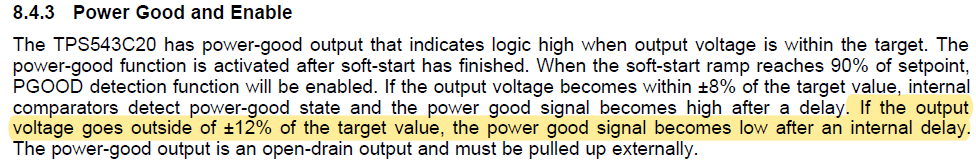

在我的测试中、在无负载条件下、输出电压需要超过1秒才能超出目标值的12%。

如果输出电压超出目标值的±12%、则电源正常信号在经过内部延迟后变为低电平。 EN 在无负载时控制 PGD?