大家好:

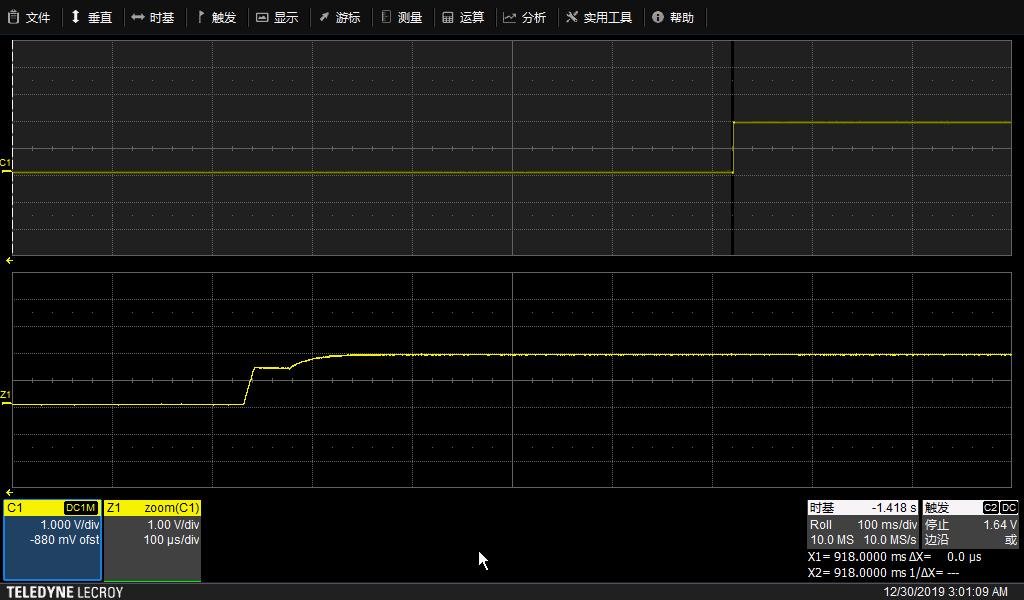

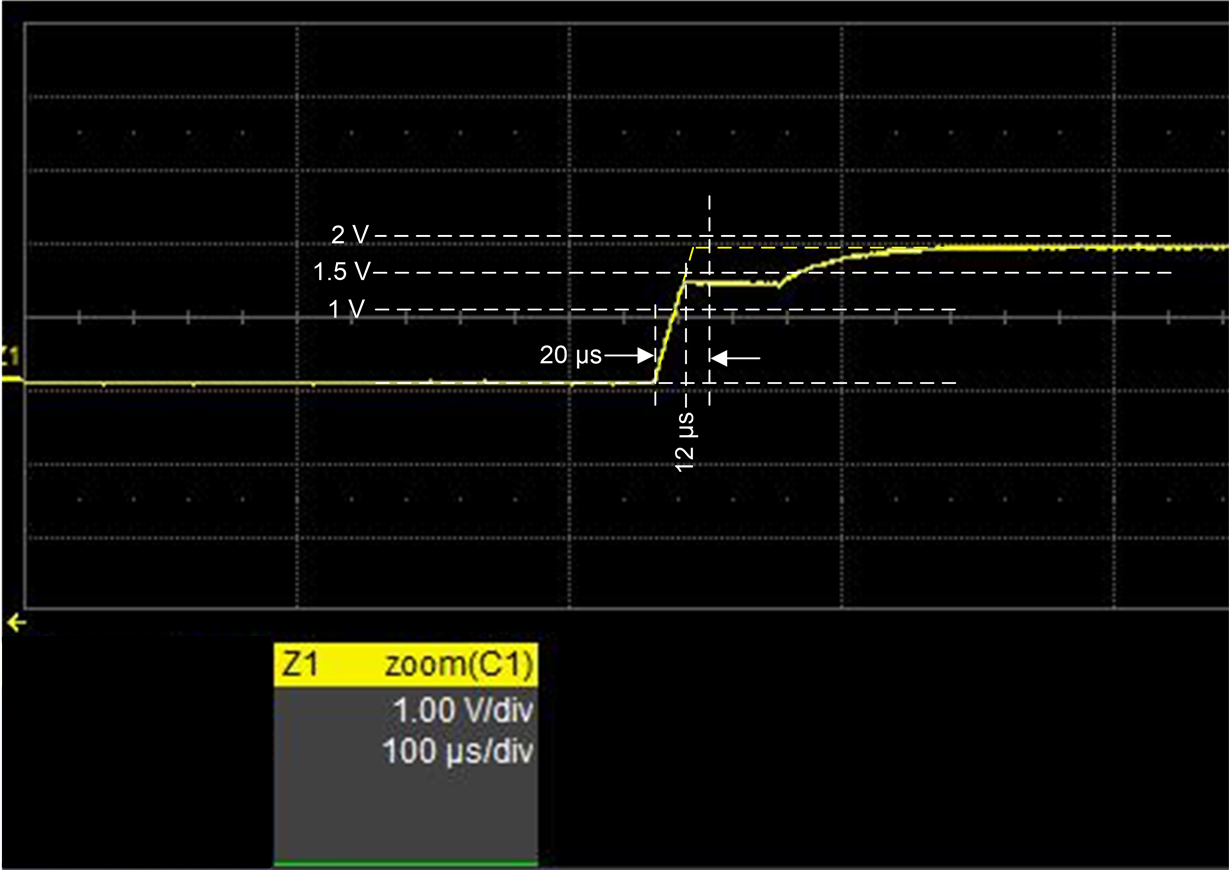

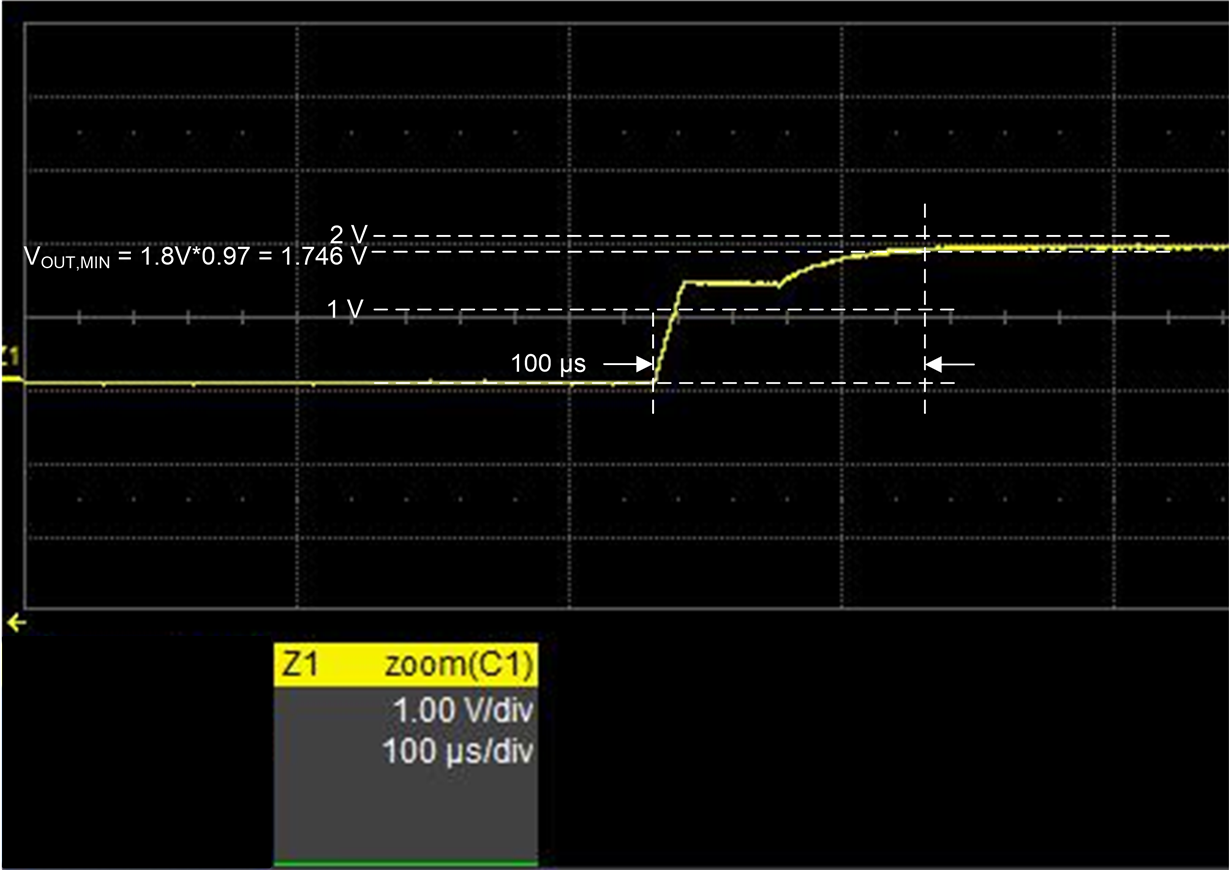

我不同意最后的结果(https://e2e.ti.com/support/power-management/f/196/t/585576?tisearch=e2e-sitesearch&keymatch=TPS65910%25252520%25252520%25252520%25252520VDIG1)、因为他 的波形不是很 准确。我 的波形是100us/div,、我看到了与 Hirotsugu Kobayashi 相同的现象(最后一个问题者)。那么、这是我的 VDIG1测试图片、它是正确的、只是一 个常规现象吗?