主题中讨论的其他器件: TPS54561

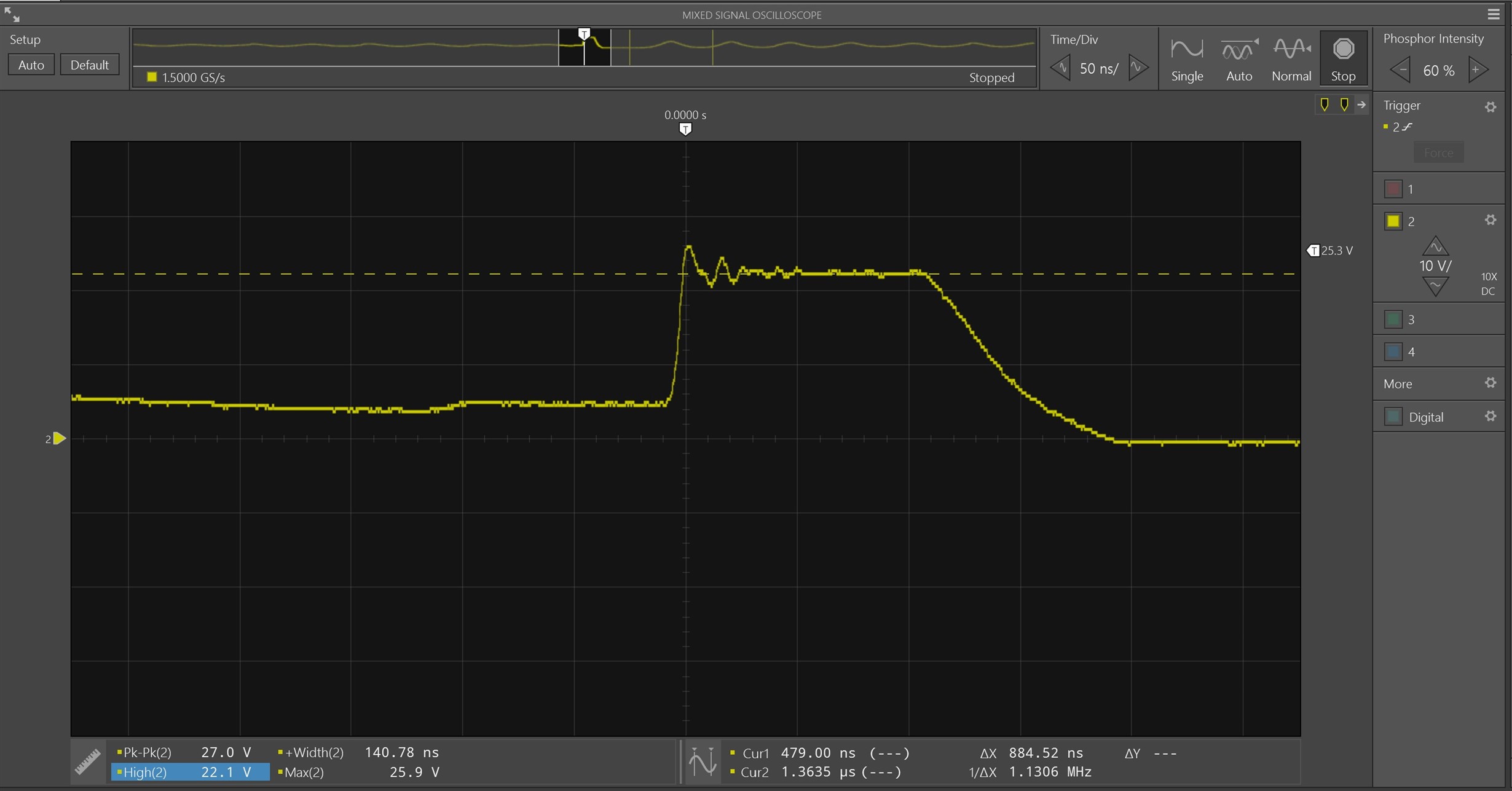

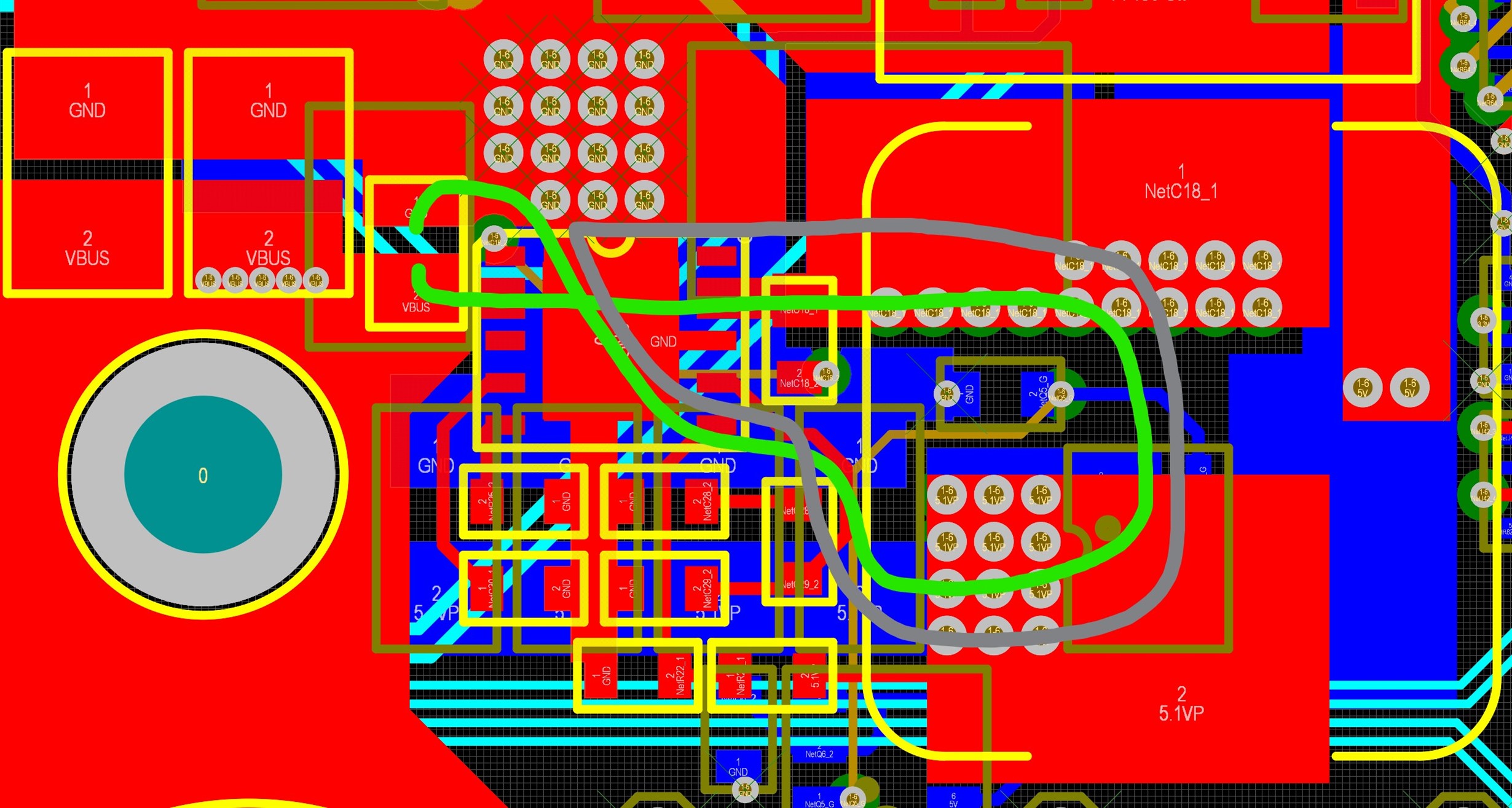

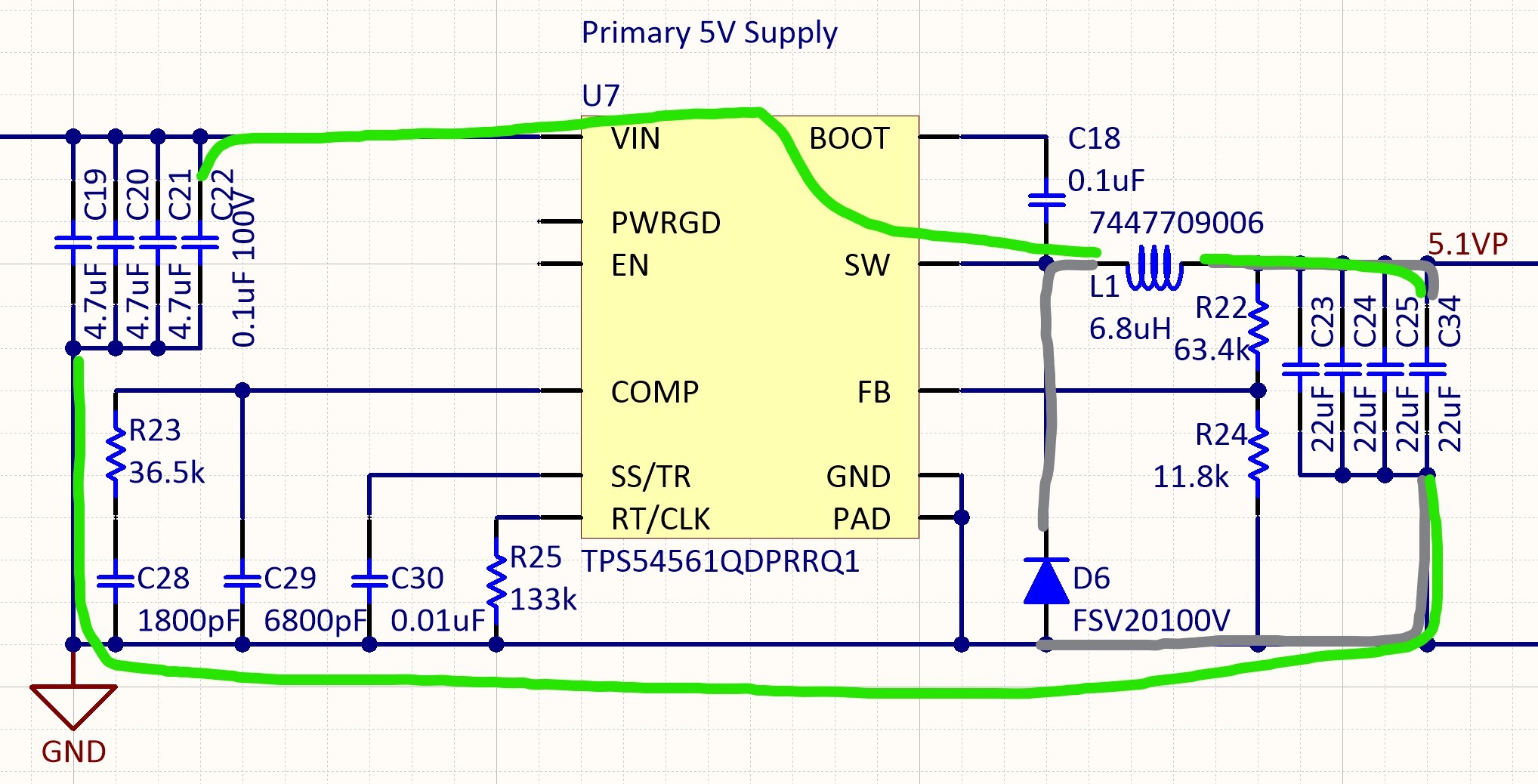

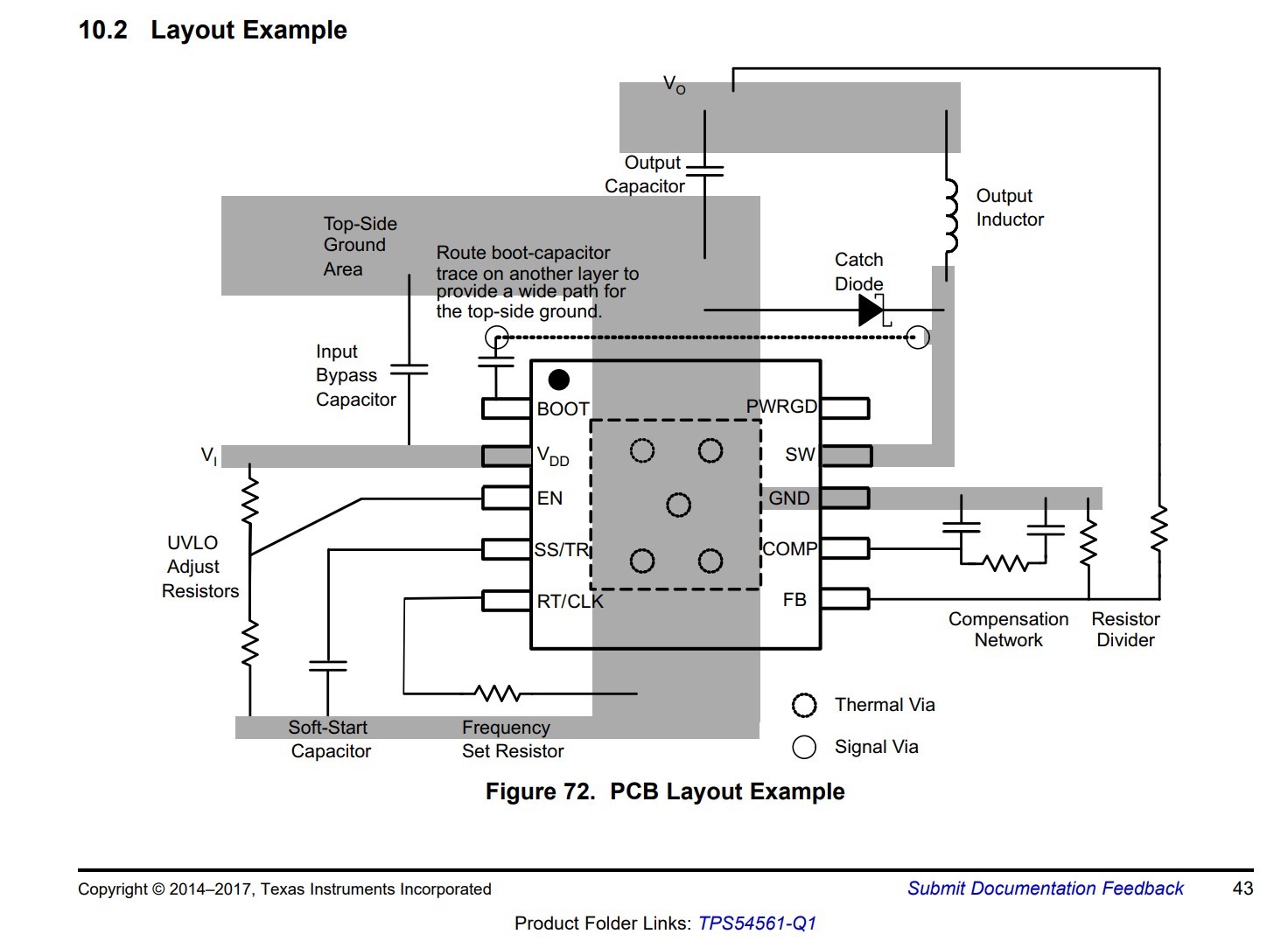

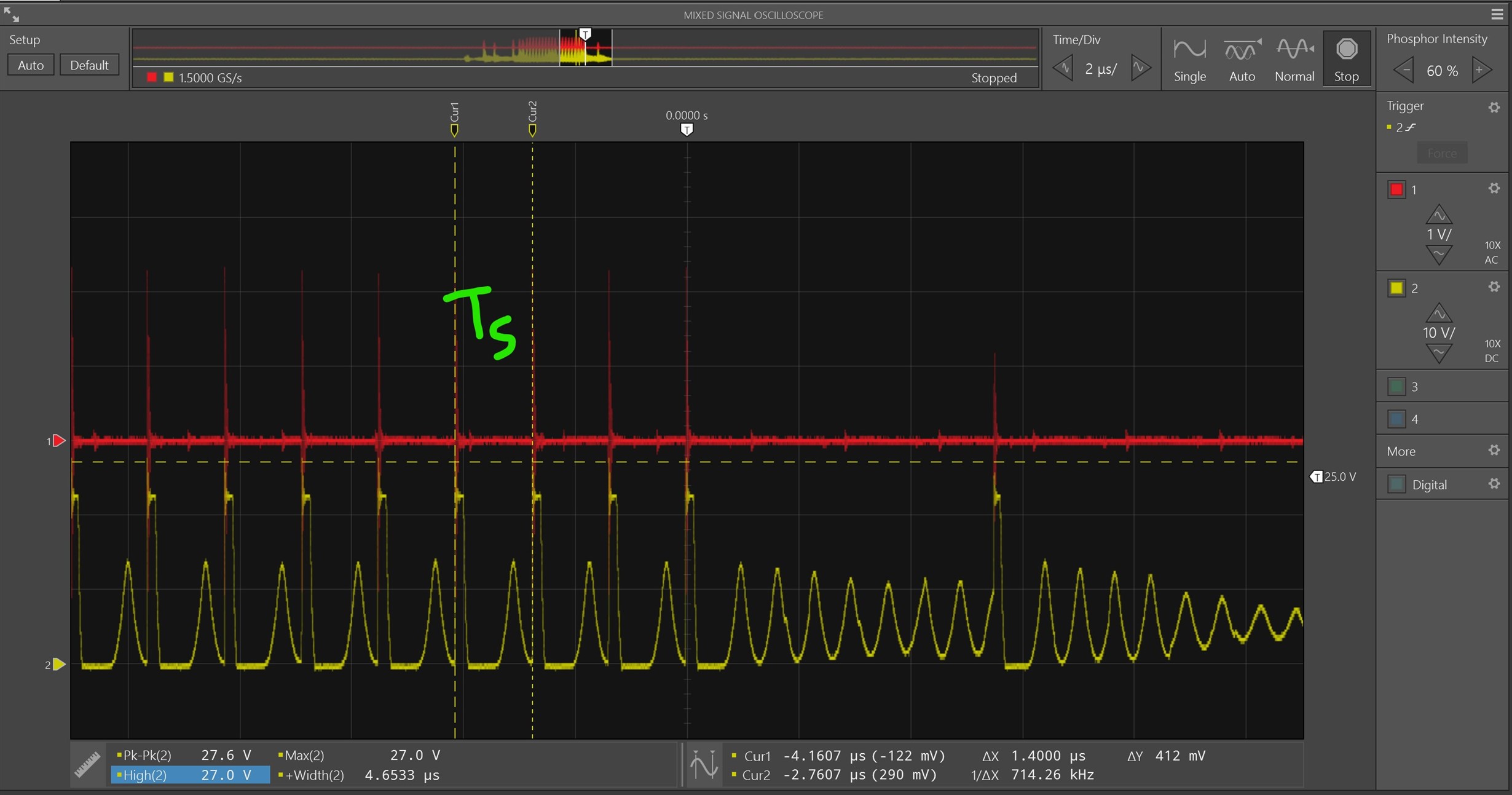

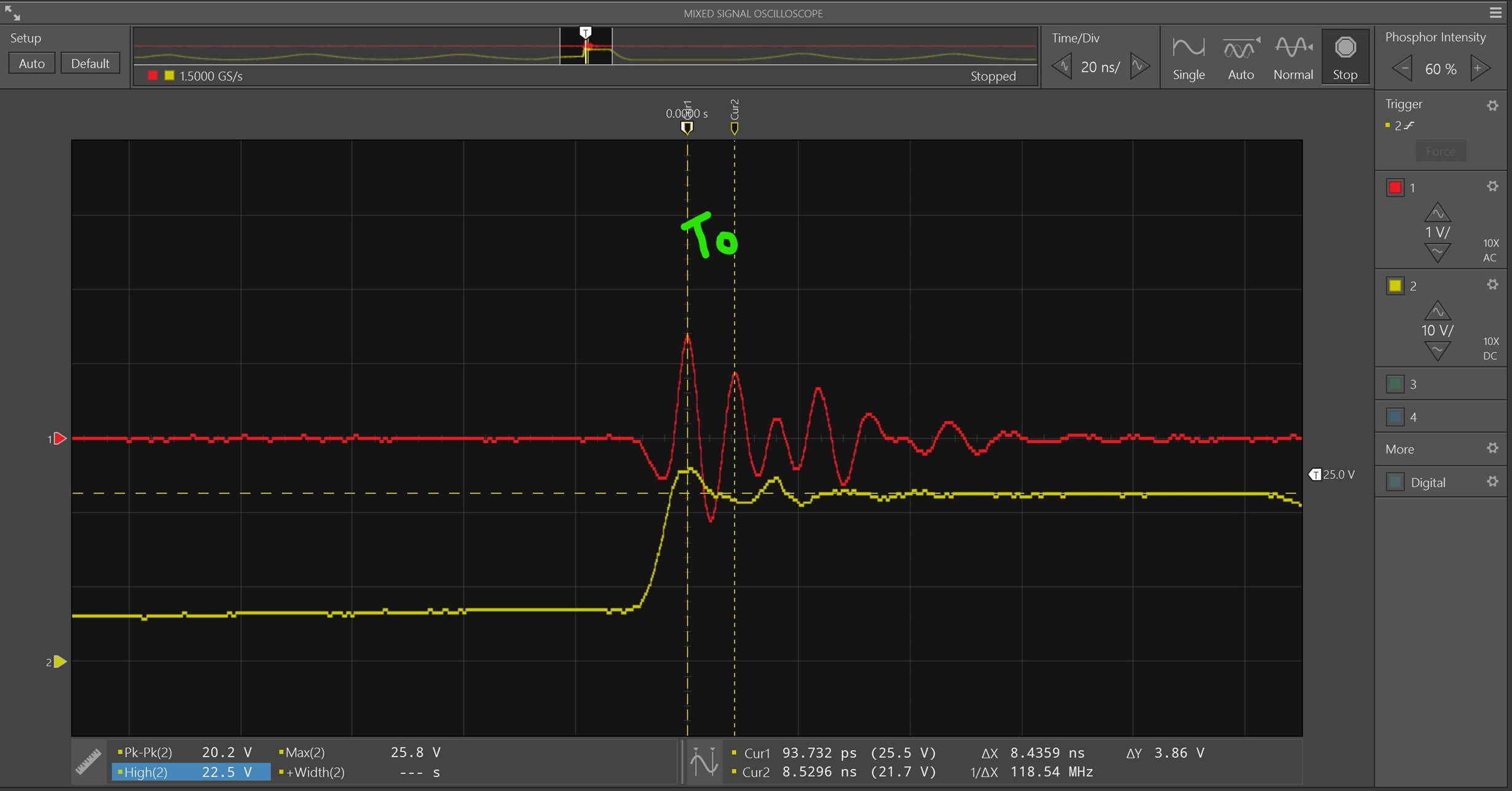

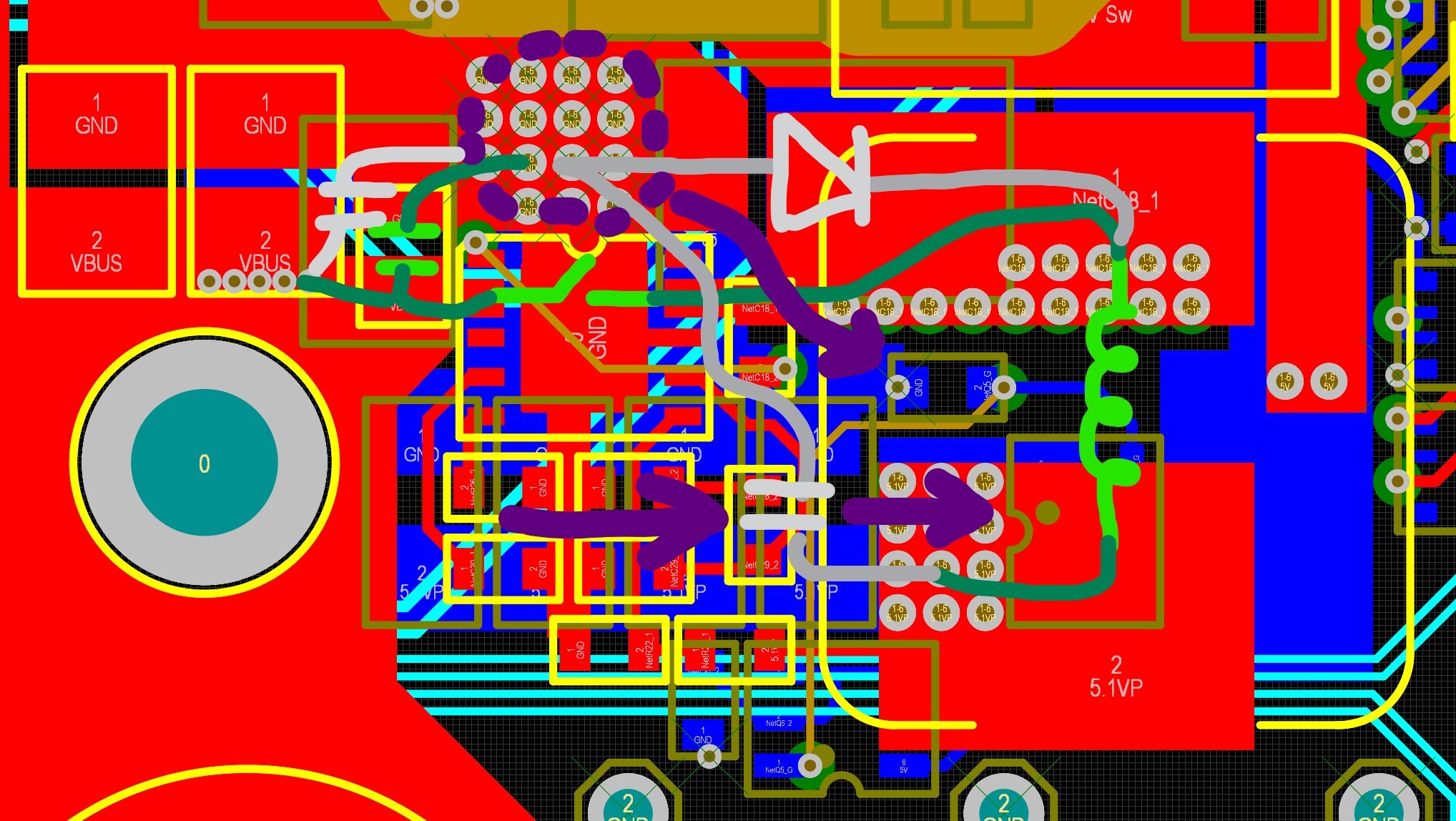

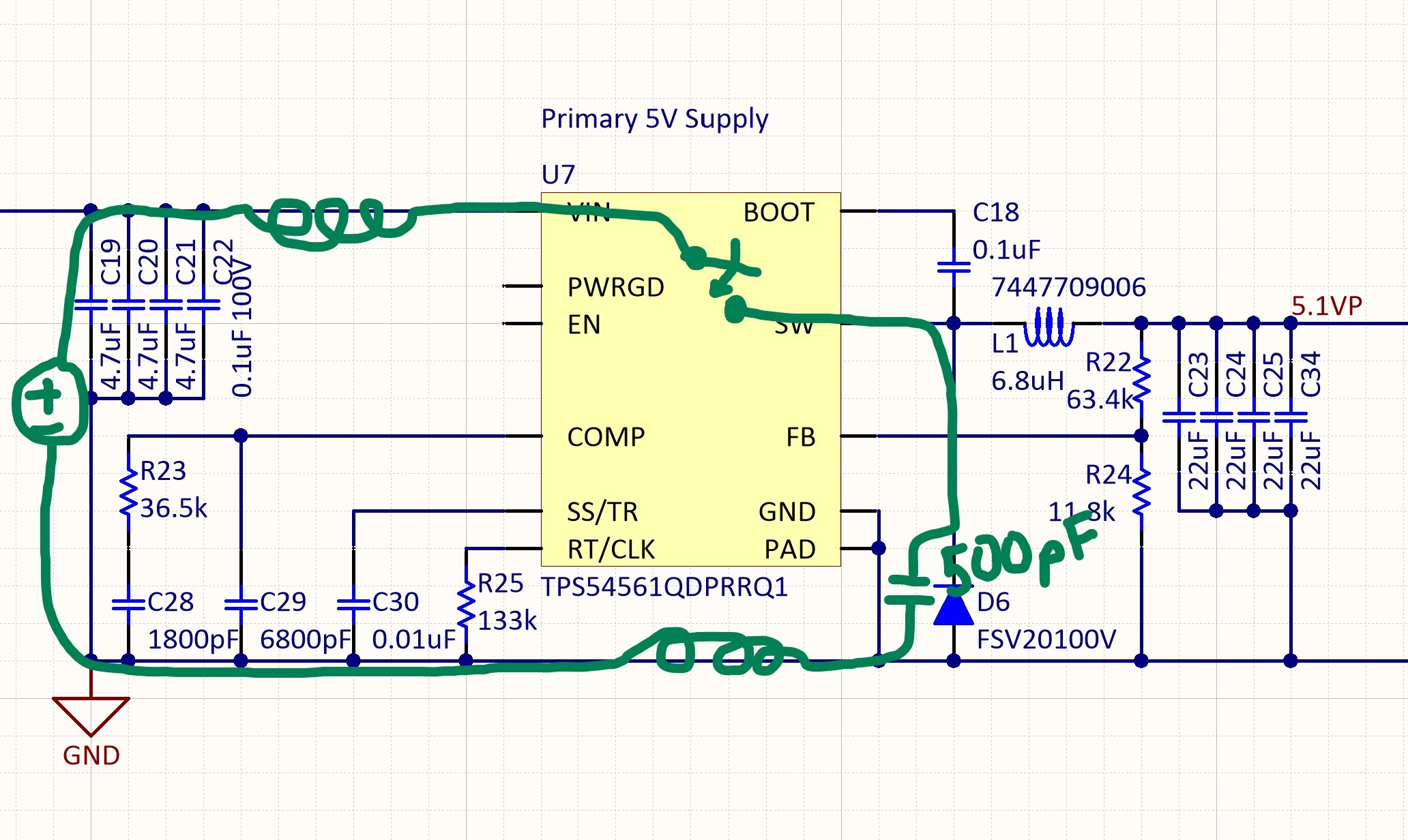

TPS54561-Q1、输入22.4V、输出5.1V。 负载最小小于10mA。 设计负载为4A。 高侧开关具有非常显著的振铃、这会导致输入电源轨上产生~3Vpp 噪声、而输出上产生~800mV 振荡。 在图2中、您可以看到过冲大约为5伏(峰值与高电平)。 布局和原理图如下所示。 我认为我需要修复布局、但我不确定如何使环路面积更小。 建议的布局如上所示。 我知道我稍微偏离了一些、但我的电感器也比布局示例中所示的大得多。 我将一些组件放在底部的问题是吗?

很高兴听到建议、谢谢。