请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LM5030 您好!

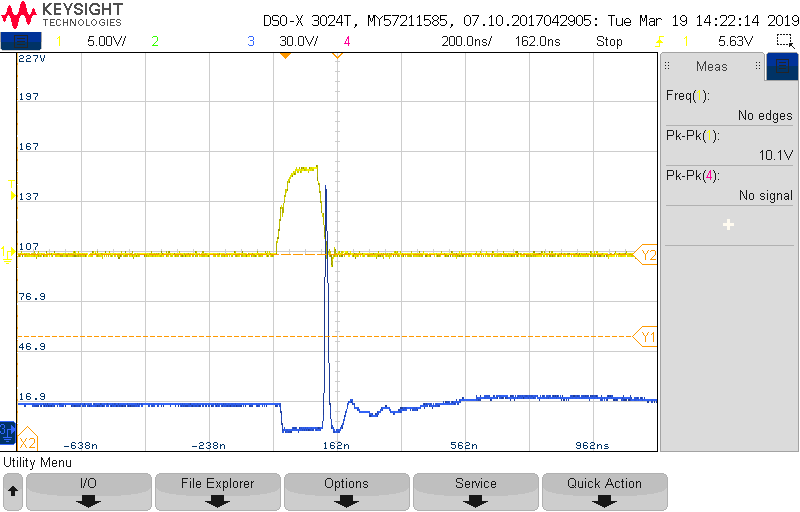

我们有一个推挽式设计、可将20-50V 输入转换为450V 输出、两个晶体管均以325kHz 的频率进行开关。 变压器的匝数比为1:23。 该设计在加载时看起来非常好、但在轻负载/短占空比下、我们遇到了问题。 在较短的占空比下、我们观察到当其中一个晶体管关闭时漏极处出现较大的电压尖峰。 该尖峰包含如此多的能量、如果可以避免、我们不希望仅仅将其缓冲。 我们不认为该尖峰与我们从漏电感中得到的已知振铃效应相同、但我们似乎不了解导致该尖峰的原因。 随着占空比的下降、它显然变得越来越糟。 对于此尖峰的合理解释、您是否有任何建议? 在较重的负载下、一切都运行得很好。 随附的示波器图显示了这些现象。 通道1 (黄色)是栅极电压、通道3 (蓝色)是漏极电压。 我们观察到、峰值最终在 MOSFET (IR 摄像头)中耗散。