降级器、

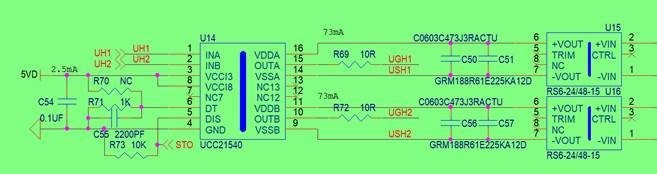

根据技术手册第21页的9.3.2输入和输出逻辑表中的规格、DT 引脚应直接连接到 VCCI。 INA 和 INB 应该是可独立控制的。 当输入为高电平时、输出也应该为高电平、但在实际测量中是如此。 当 INA 和 INB 都为高电平时、两个通道的输出都为低电平、即无法实现真值表中连接到 VCCI 的 DT 逻辑。

在测试过程中、注意 DT 引脚的电压。 连接到 RC 时的测量值约为0.8V、连接到 VCCI 时的测量值约为4.98V。 此外、在电路设计中、DIS 引脚接地至10K 电阻器、测试期间始终存在电阻。 当输入 INA 和 INB 不为高电平时、输出逻辑与输入一样、理论上芯片可以工作。

请帮助我确定无法实现逻辑的原因。

谢谢!