您好!

我使用 TPS56C21进行设计、这些是 webench 电源设计人员推荐的主要稳压器参数:

输入电压:12V、 输出电压:1.0V

输出电流:8安培

fsw:400kHz (由我选择、以降低 IC 功耗)

L:1u2

COUT: 9 x 47uF (MLCC-

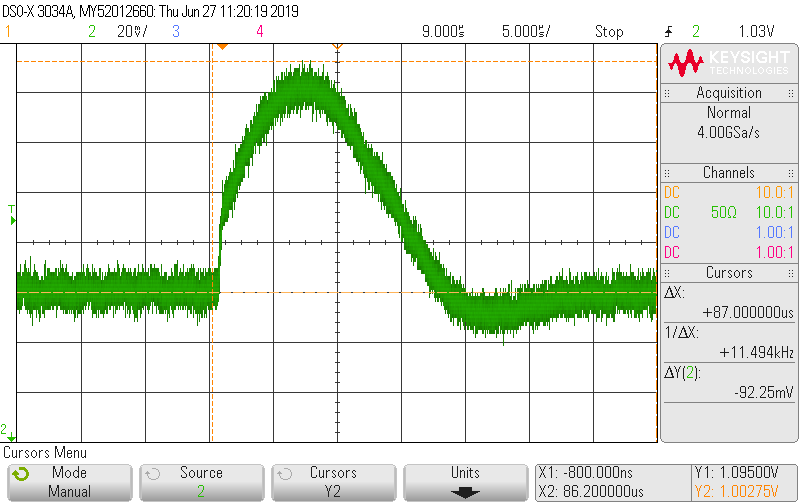

此设计可驱动 FPGA 电源轨。 在工作台测试中、我注意到 FPGA 结束代码配置时出现了快速的大型负载瞬态。稳压器大容量电容不足以在 IC 发生反应之前吸收该瞬态、从而使1V0电源轨接近1V1、即 FPGA 的绝对最大值。

我认为、瞬态完全是由于没有大容量电容。 将 SW 频率更改为800kHz 似乎没有什么帮助。 将大容量电容从423uF 增加到900uF (9 x 100uF)(MLCC–ESR:2m Ω)可将过冲降低到60mV、而不存在明显的稳定性问题。

我注意到 TPS56C215规格表中的最大限制为500uF。 我想保守地说,将 Cout 增加到600uF (6 x 100uF)。 我的问题是:

- 600uF 在一个电路中工作正常、我有多大信心不会出现稳定性问题?

- 是否有一种简单的方法来确定600uF 的稳定性裕度? (webench Designer 不允许我超过500uF)

谢谢、

JMR