您好!

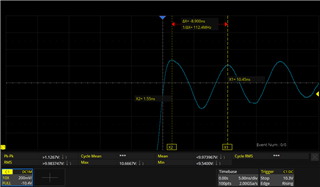

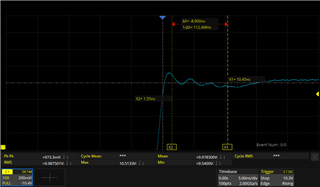

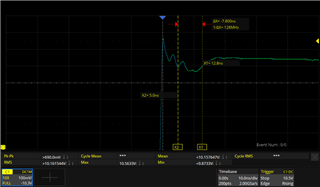

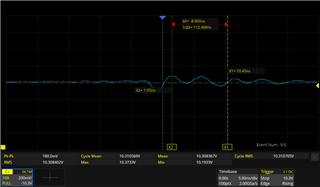

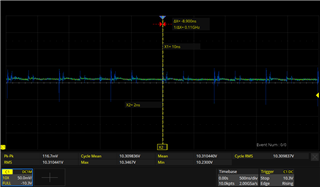

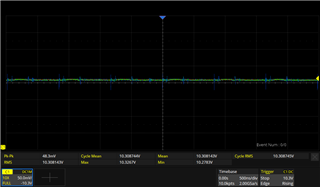

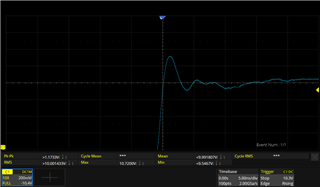

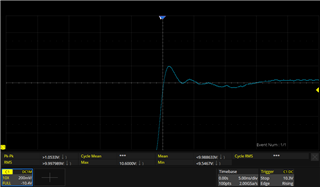

我遇到与 user6371168 (https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/937718/tps65150-tps65150)相同的 AVDD 噪声问题。 空载时噪声更大。 无负载时情况更好、但仍然很重要。 在阅读 了辽家汗在这个主题中的支持后、我重新设计了 PCB、但问题仍然存在。

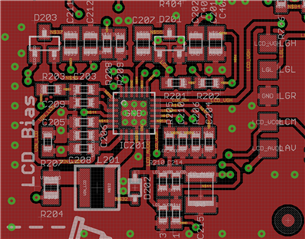

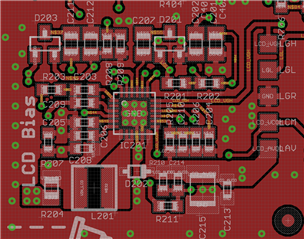

第一个 PCB 只有两层铜、一个接地。 第二次重新设计具有4层(第1个信号+接地、第2个接地、第3个电源、第4个信号+接地)、并通过0r 电阻器将接地(电源接地和模拟接地)分离在一个点上。 两个电路板上都存在相同的问题。 因此、组件可能存在问题...

有关原理图和布局、请参阅附件。

我在 AVDD 上尝试了两种类型的二极管(D202)。 首款更便宜的 TS4148 RYG 和第二款更昂贵、更快的 PMEG3010CEJ 都在 PCB 设计上实现、但没有效果。

不知道问题在哪里... 感谢您的支持。