您好!

我的供应商要求我将阻焊层开孔增大到焊盘尺寸。

https://www.ti.com/lit/ml/qfnd355c/qfnd355c.pdf

我在 DQN0004A 的图纸之后创建了封装。

现在、供应商很难在引脚1至4的阻焊层中创建小开孔。 他要求我将阻焊层增加到焊盘尺寸。

阻焊层的这种更大开度是否会影响可焊性或您的侧有其他机械问题?

电气上、它不应产生任何影响。

此致、

David

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我的供应商要求我将阻焊层开孔增大到焊盘尺寸。

https://www.ti.com/lit/ml/qfnd355c/qfnd355c.pdf

我在 DQN0004A 的图纸之后创建了封装。

现在、供应商很难在引脚1至4的阻焊层中创建小开孔。 他要求我将阻焊层增加到焊盘尺寸。

阻焊层的这种更大开度是否会影响可焊性或您的侧有其他机械问题?

电气上、它不应产生任何影响。

此致、

David

尊敬的 Edgar:

我指的是电路板布局。

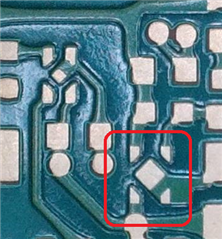

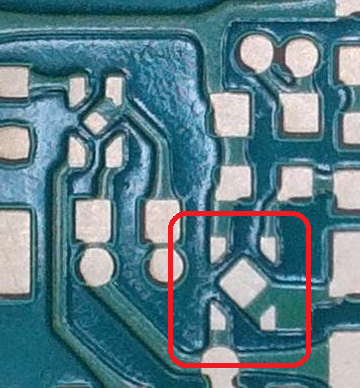

如图所示、阻焊层开孔是相关主题。

我的供应商说它很小、我应该将其增加到阻焊层下的金属尺寸。

我同样担心短路的潜在风险。 但焊锡膏量不会增加。

我希望您能从 X2SON 封装开发中获得一些有关不同供应商阻焊层应用工艺的变化和容差的数据、您会说:"这不是数据表中所示的理想产品、但目前还不知道这是一个问题。"

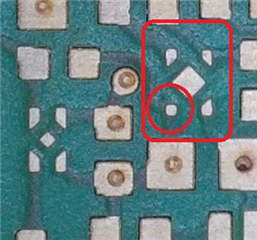

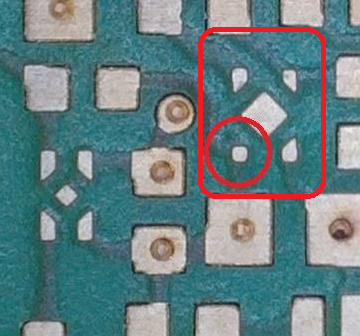

或另一种方式... 以下图片显示了我从供应商处获得的信息。 他说、PCB 在公差范围内、从公差的角度来看、右图中的焊盘没有问题。 您知道 X2SON 封装会发生这种情况吗? 这个较小的开孔是否仍在要正确焊接的 X2SON 封装的容差范围内?

在编写完上述所有内容后、我想我的实际问题是:我能否保持数据表中所示的封装尺寸、阻焊层开孔是否可以接受、或者我是否应该增加阻焊层开孔、并确保我的供应商能够与之配合使用。

或者最后我必须自己解决这个问题?

提前感谢您提供任何信息。

此致、

David

我想答案将类似于以下帖子:

e2e.ti.com/.../bq25101-land-pattern-design---non-solder-mask-defined-for-dsbga-and-x2son

尊敬的 David:

这张图片对我来说似乎是正确的:

我们在 DS 中展示的只是示例和指导、这也是我们在设计 EVM 时使用的内容。

这也取决于每个供应商及其能力、但我们知道、有些容差将与 DS 中显示的容差略有不同、但我没有遇到任何问题。

我会更担心以下图像:

可能不足以正确焊接器件的应用。

我可以由包装团队执行此操作、以查看他们是否对此有任何想法/顾虑。

最棒的

Edgar Acosta