我有一位客户看到 UCC27533的以下问题:

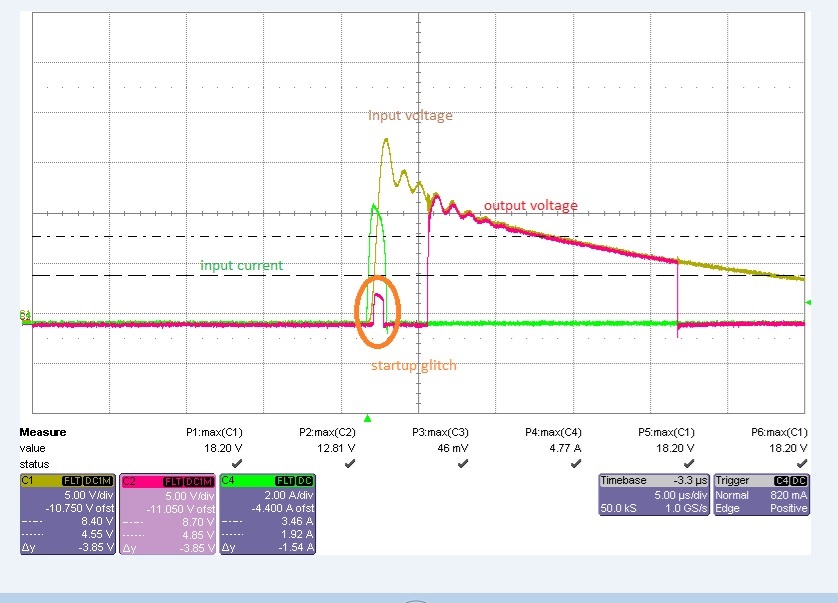

我的电路非常简单。 VDD 和 IN+连接在一起。 IN-和 GND 连接在一起。 在 VDD 和 GND 之间放置一个100N 的去耦电容器。 我的应用使该电路通过三角脉冲激励。 在 VDD 上的电压斜升期间、我在输出端看到一个小脉冲。 这是在电压升高到 UCC27533的工作电压之前发生的。 我使用 IC 模型在 TINA 中模拟了同一电路、但我看不到这种情况。 如果您能在这方面为我提供帮助、我将不胜感激。 启动操作是否无干扰? 我看到了另一个类似的驱动器、其中特别提到了无干扰启动。

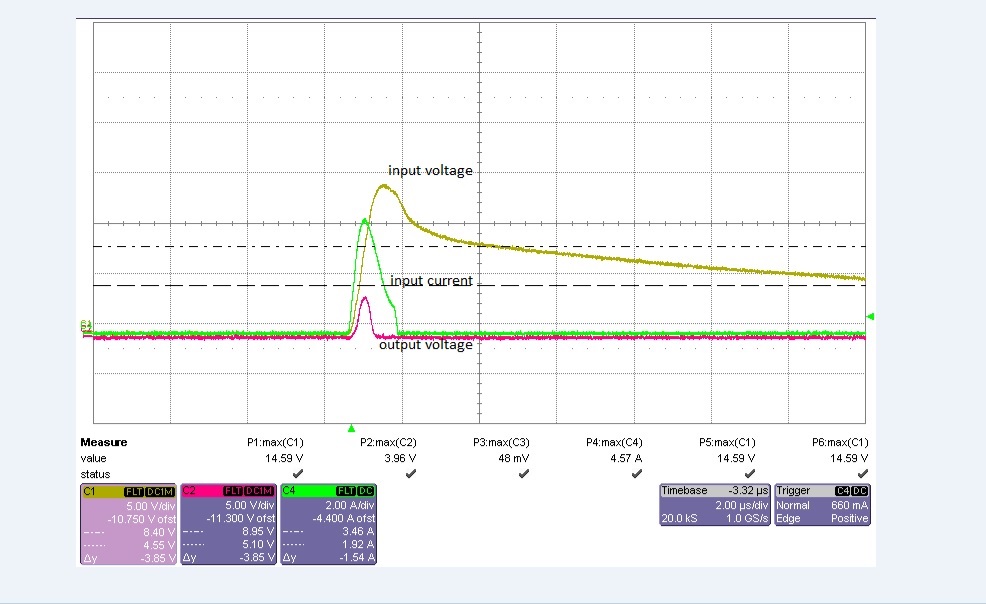

我在前面的示波器屏幕截图中显示的电流是为去耦电容器充电的电流。 该电流可能尚未经过 IN+的下拉电阻器。 我已提起 IN+并将其保持打开状态;根据任何输入断开时的数据表、输出应处于低电平。 我确实看到干扰部件仍在出现。

根据功能方框图、无论输入端的逻辑电平如何、只要 VDD 小于工作电压(8-9V)、输出就应该为低电平。 在远低于电压的情况下会发生干扰。

在我看来,在这一部分的启动过程中不应该有一个“毛刺脉冲”。 您能否查看此问题并让我知道您认为正在发生什么?

感谢您对此的帮助!

Richard Elmquist