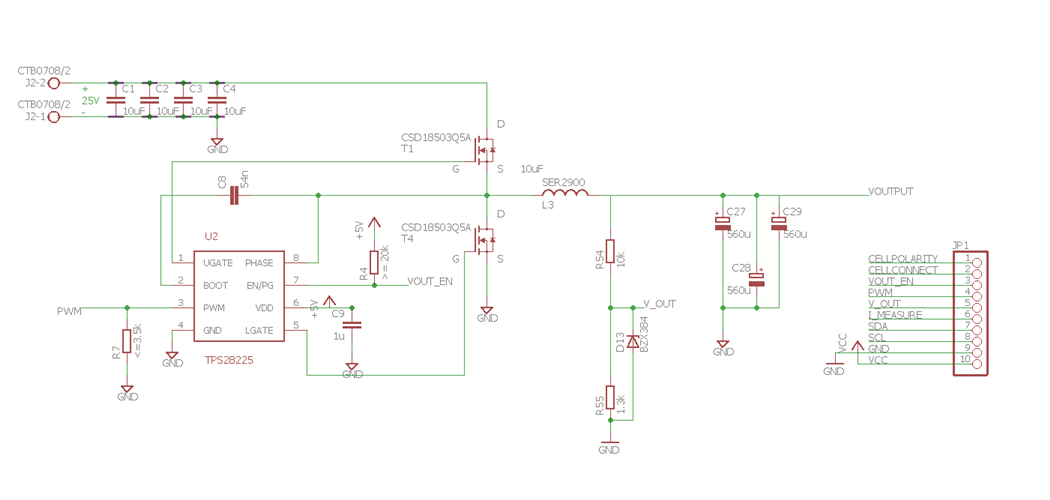

我正在设计基于 TPS28225的直流/直流转换器。 当由 VDD=4.5V 供电时、输出是干净的、但是当将 VDD 增加到5V 时、输出电压会降低到5V 并产生很大的噪声。 FET 也会耗散更多的热量。

这些结果通过以下参数实现:

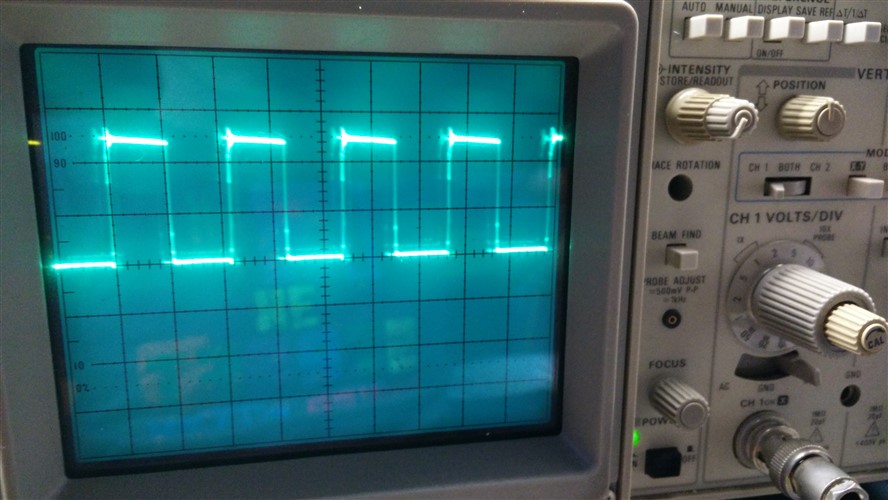

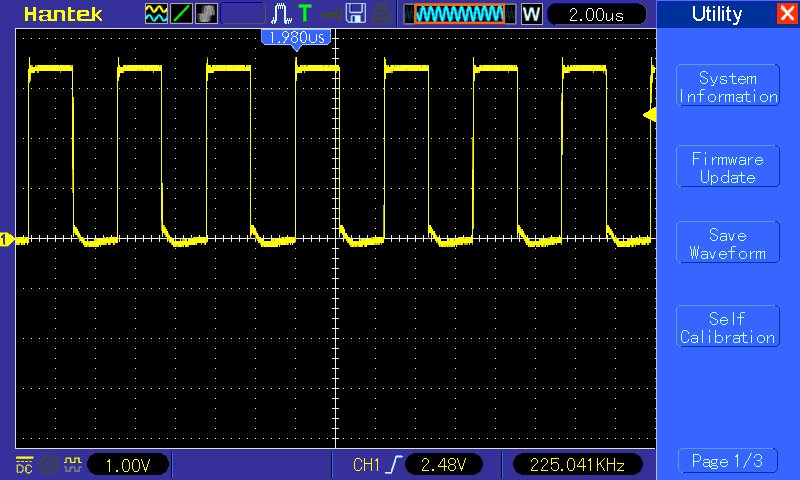

PWM:F=226kHz、D=50%、3.4V

EN = 3.4V

VIN = 25V

我似乎无法找到有关在增大 VDD 时输出噪声的原因的解释。 我尝试使用较大的自举电容器(100nF)、但它没有产生任何影响。

出于实际原因、我希望能够使用5V 电压为驱动器供电。

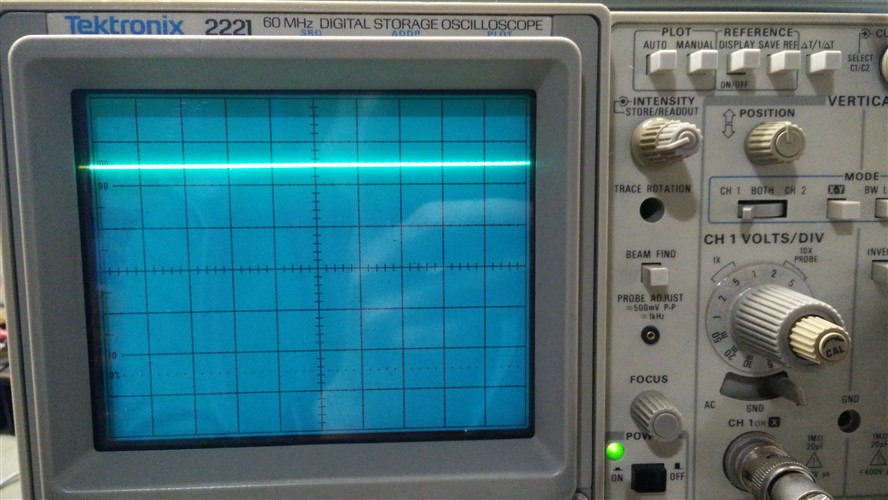

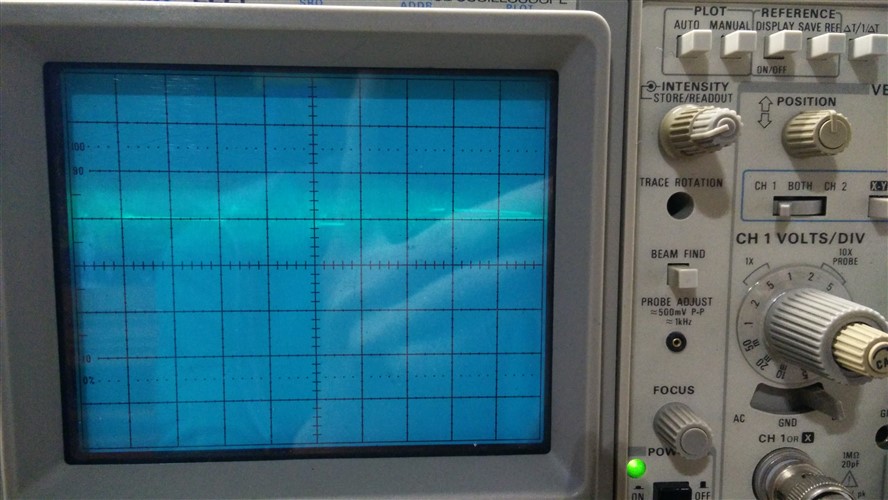

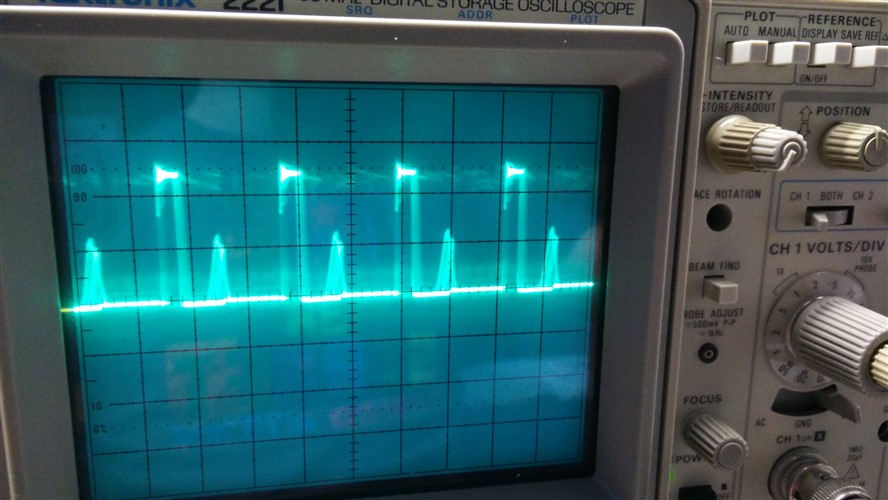

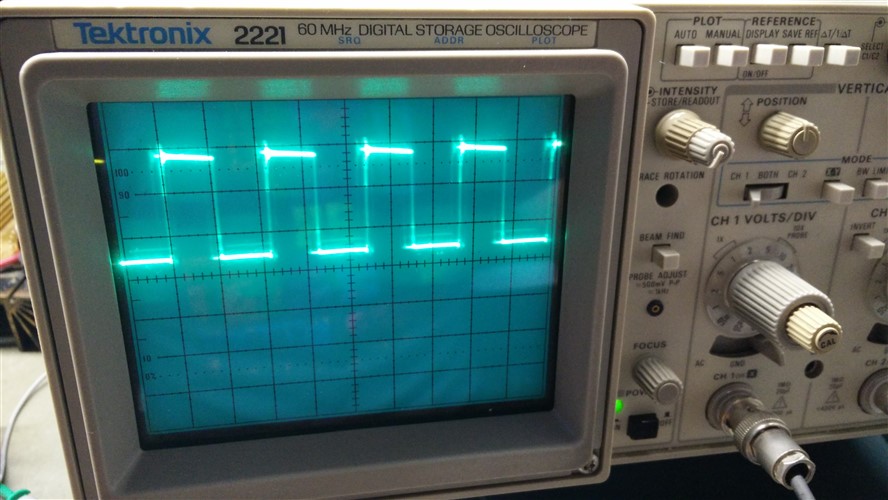

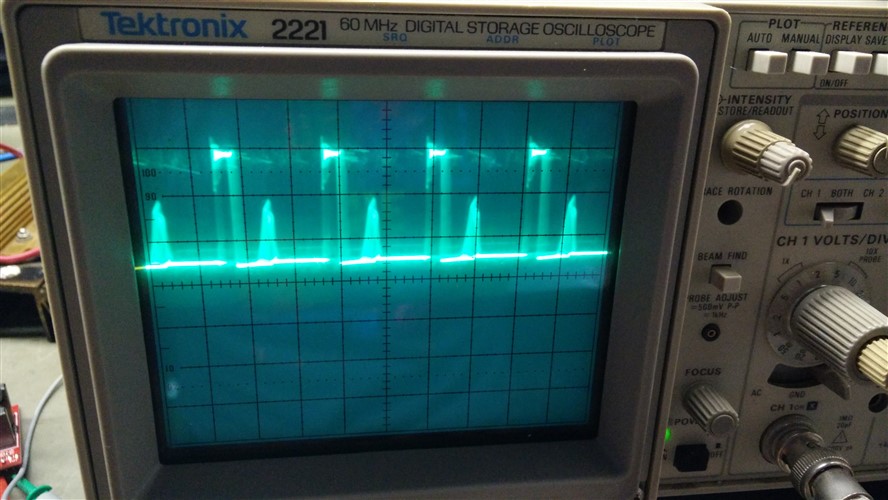

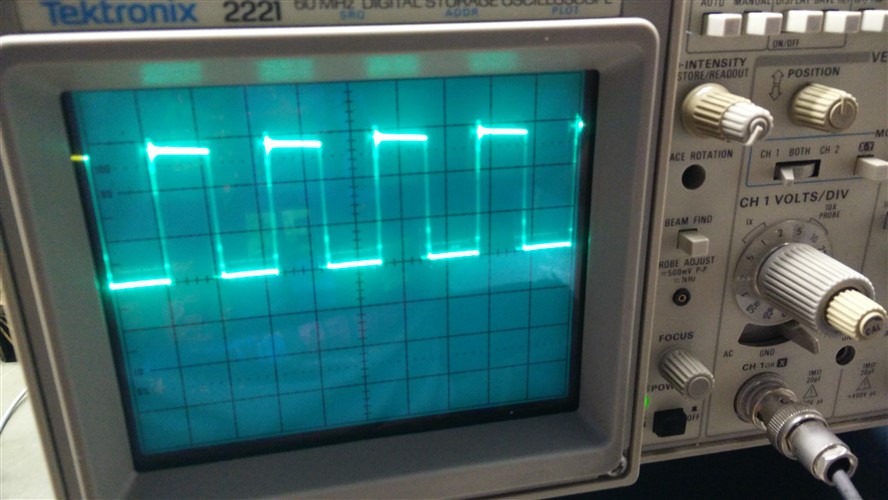

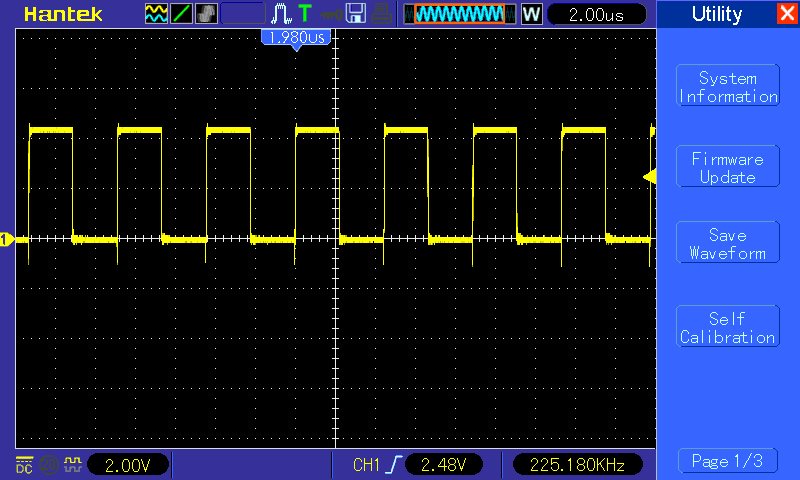

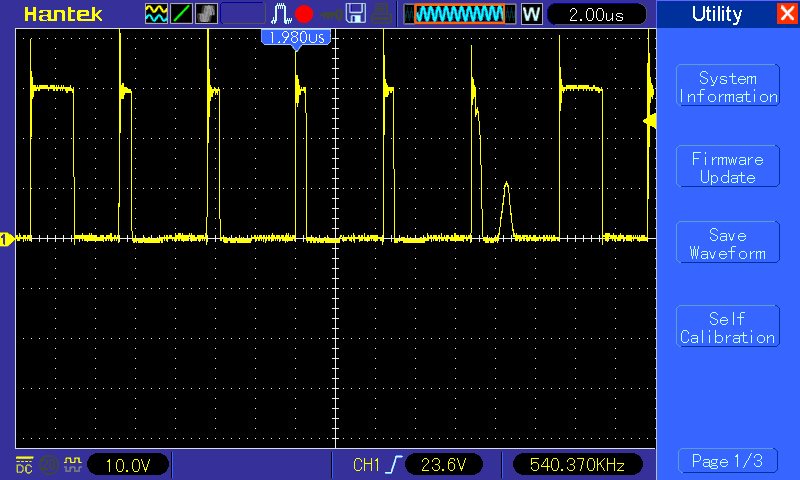

随附示波器图像和原理图。 将会得到任何帮助。

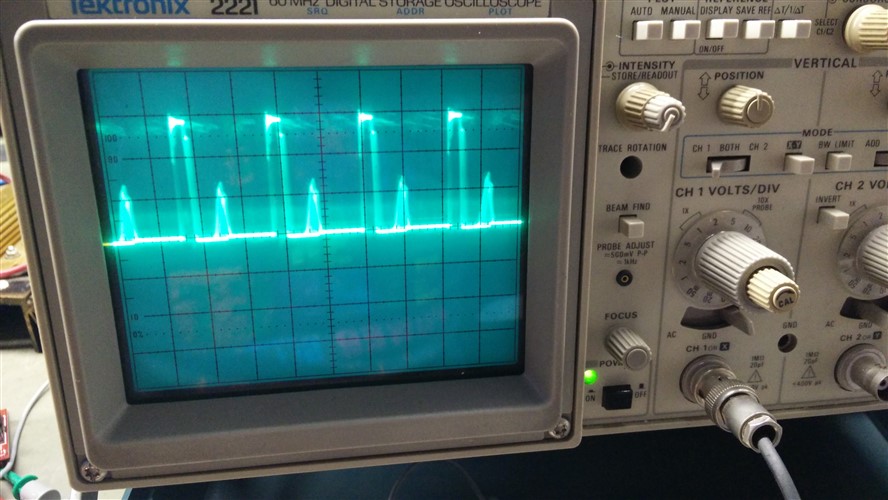

VDD=4.5V、V/div =5V S/div =10us

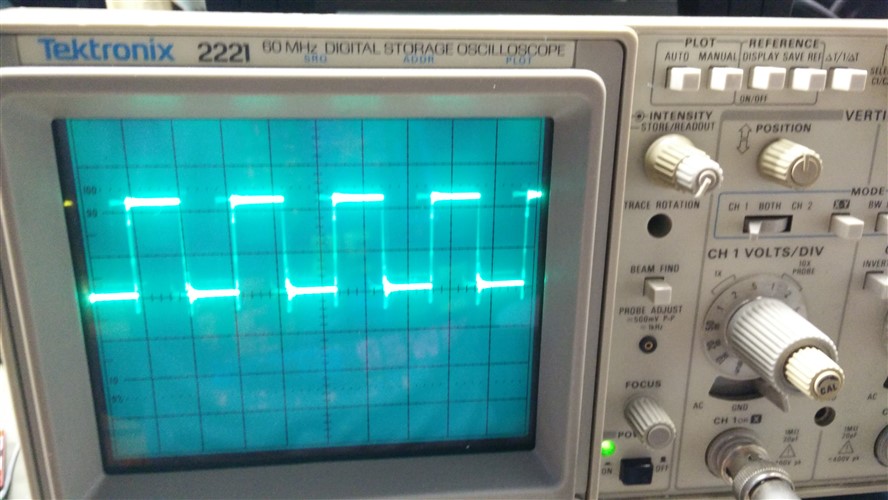

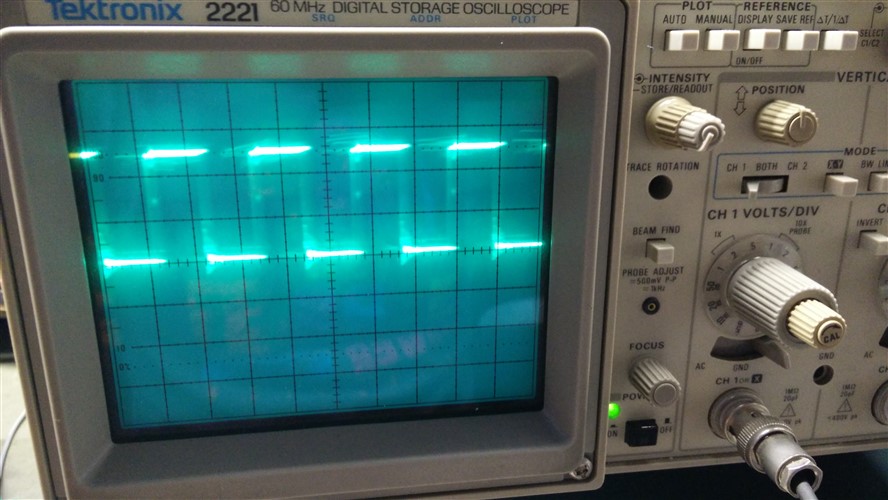

VDD=5V、V/div=5V S/div=10us