主题中讨论的其他器件:UCD74120、 UCD9244

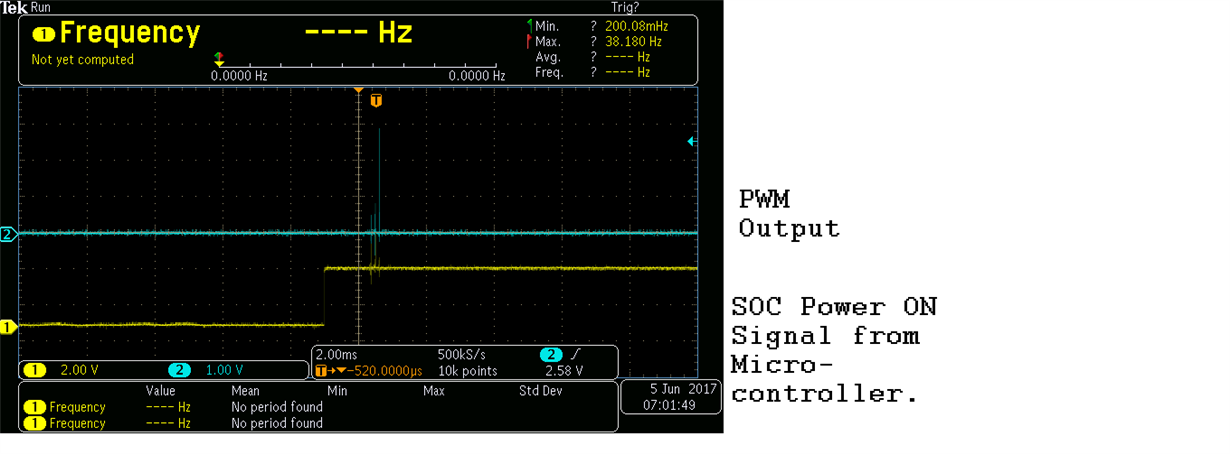

我们组装了电路板、并在为 SOC (K2K)供电时遇到问题。 我们一直在微控制器的 LCD 上看到 SOC 电源故障。我们已确保所有使用的 UCD 文件都是最新的。 我们从 Advantech 网站上选择了它。

UCD 配置从以下链接中获取。

http://www2.advantech.com/Support/TI-Evm/EVMK2HX_sd4.aspx

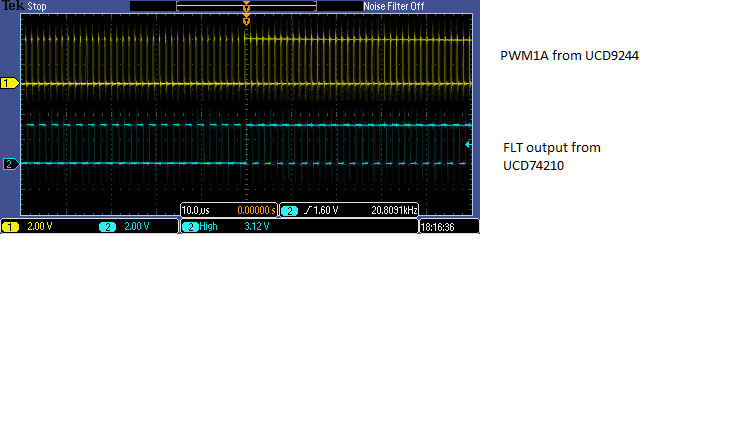

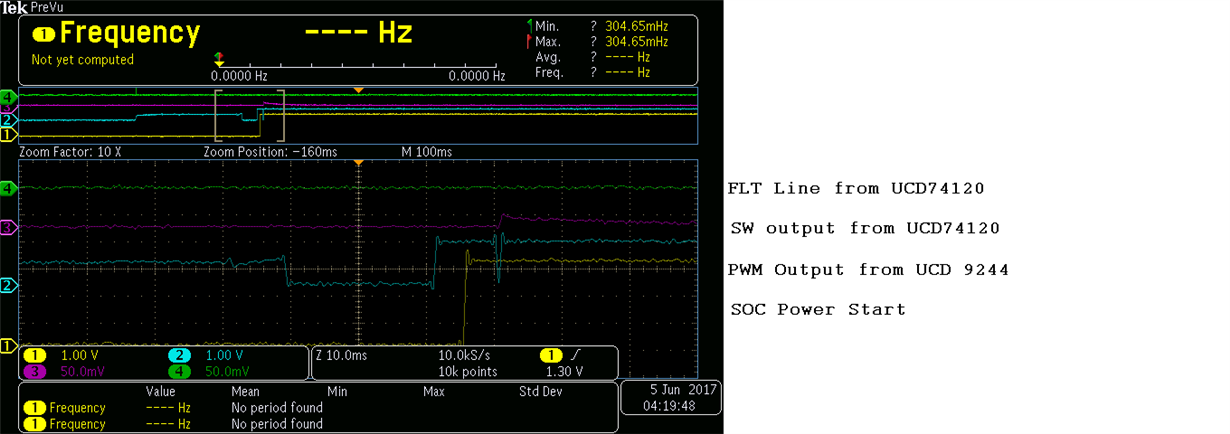

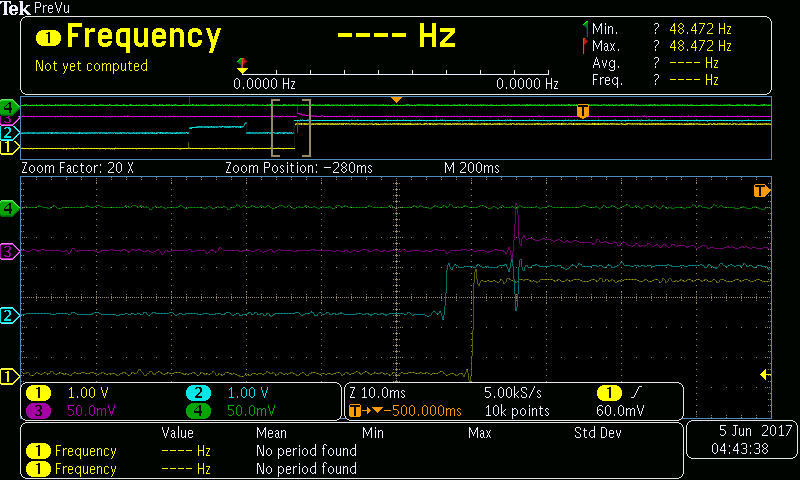

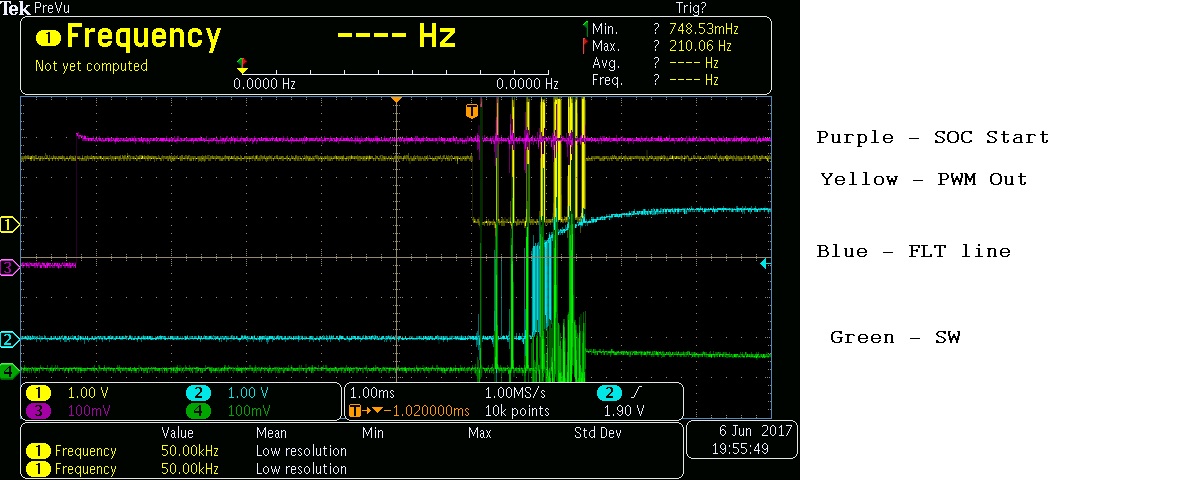

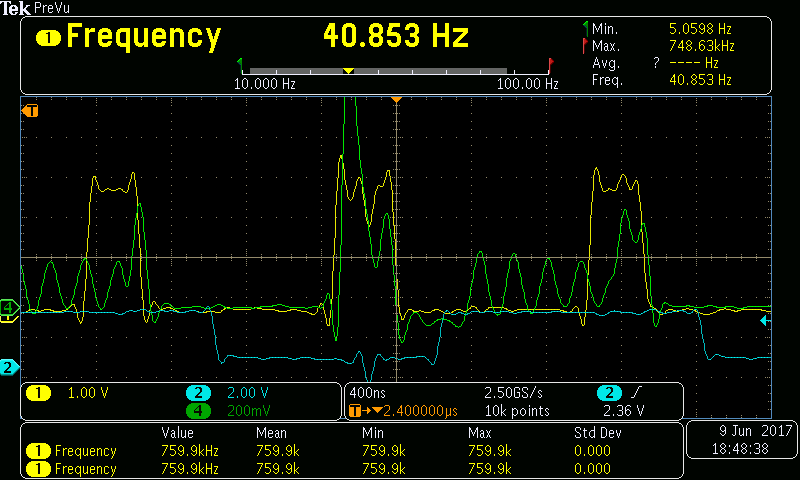

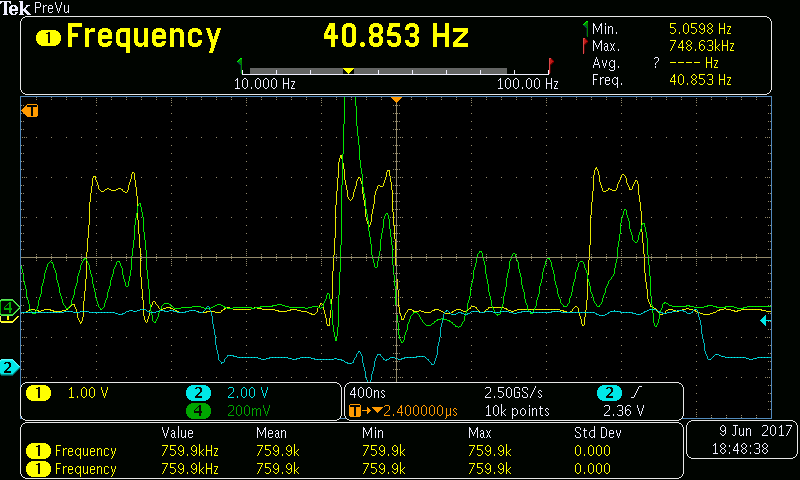

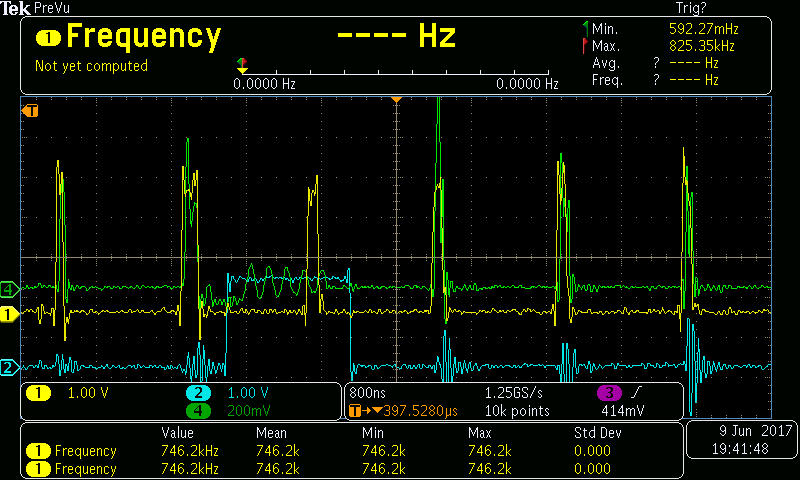

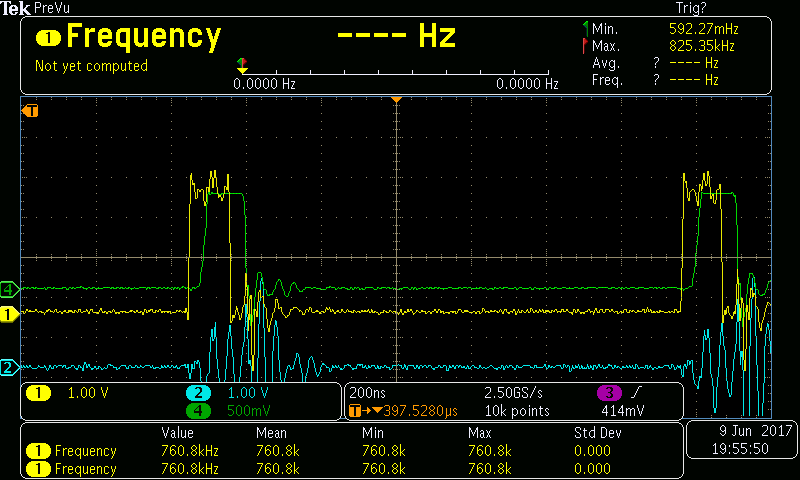

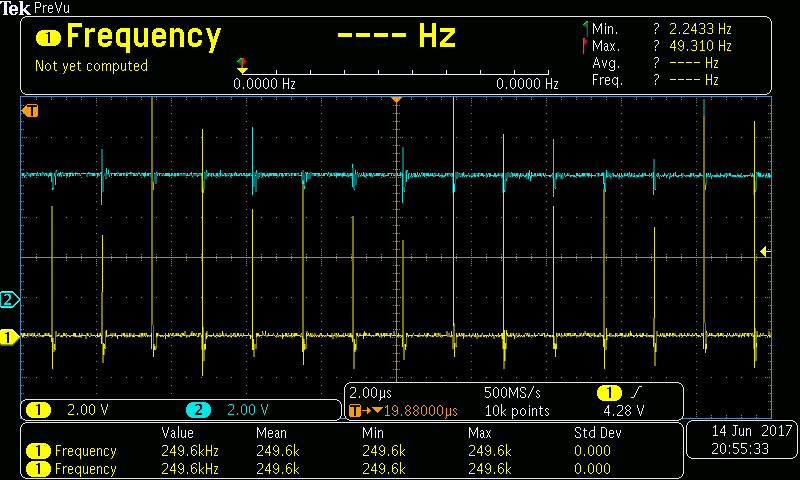

在 UCD9224上、我们看到两个电源轨都报告来自 UCD74120的 FLT 线路。 PFA 原理图和示波器图、描绘具有 PWM 输出的 FLT 线路行为。

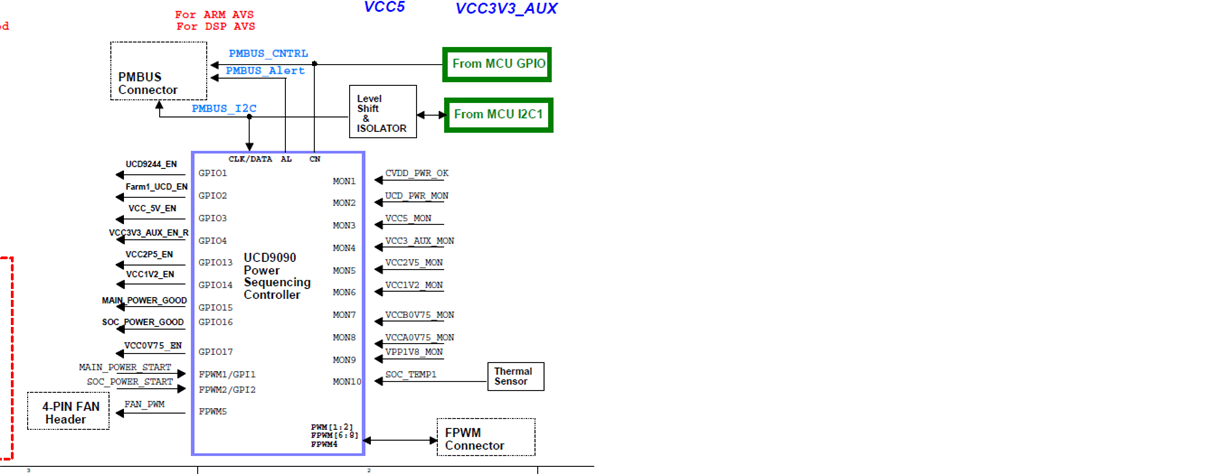

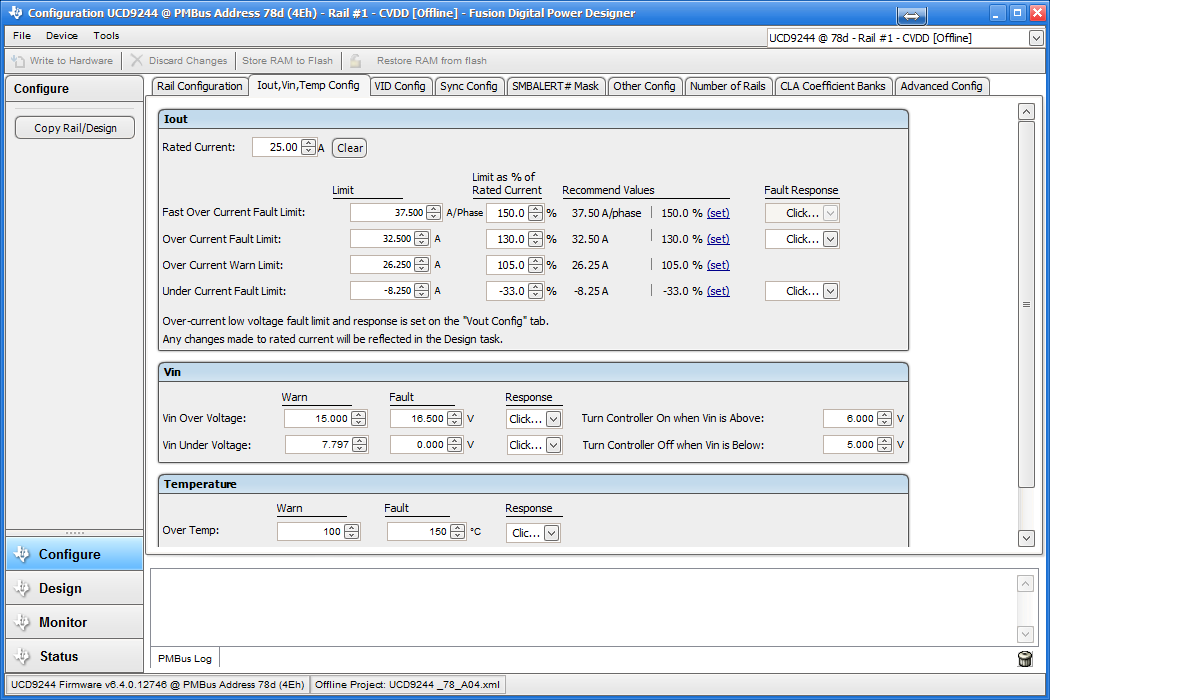

下面是所使用的电源设计方案。 我们已重复使用 Advantech 的 K2K EVM 的设计。

我们观察到 FLT 线在 PWM 周期期间振荡。 随附示波器捕获、原理图和 Fusion 软件 capturese2e.ti.com/.../6574.UCD9244-6.4.0.12746-Address-78.docxe2e.ti.com/.../K2K_2D00_CVDD_2D00_PWR_2D00_Section_2D00_Sch.pdf