主题中讨论的其他器件:TIDA-00778、

您好!

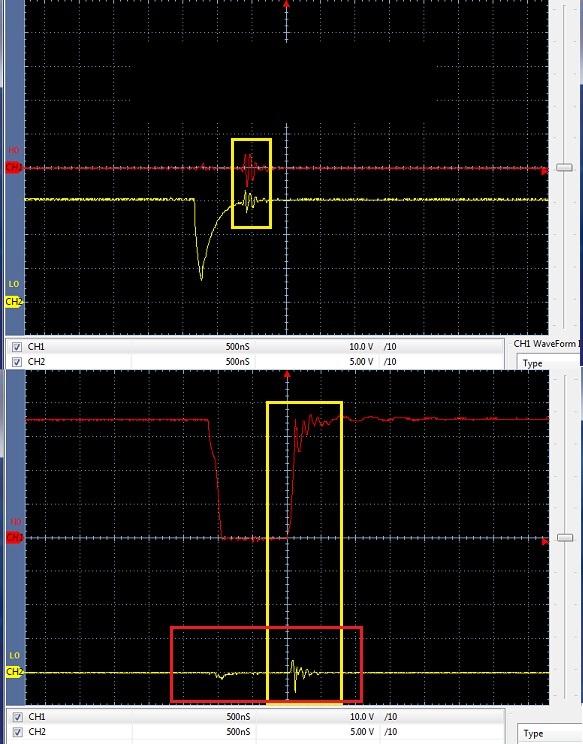

请帮助确定为什么同步死区延迟 (80ns) HO 下降、LO 上升沿似乎会在 HO 下降/上升脉冲期间沿接地(-5-10V)引起 LO 振铃。 当死区立即更新时、 LO 下降/上升沿 会在 LO 低脉冲时间内引起 HO 环残留脉冲。 HI/LI 输入上的重叠 PWM 信号驱动 HO/LO 输出只在 最后一个 PWM 周期 Ton NFETS 上产生死区延迟。 NFETS 上的最后一个 存在于 三个 UCC 中的两个、 一个是高侧、一个是低侧。

可能内部爬电 或 间接 HI/LI 会在 相反输出端造成死区延迟残留? HI/LI 输入滤波器(200pf/51ohm)是否 会导致 AGND 上 LO 通过 COM 拾取的串扰?

如何 缓解 HO/LO 死区残留振铃脉冲?