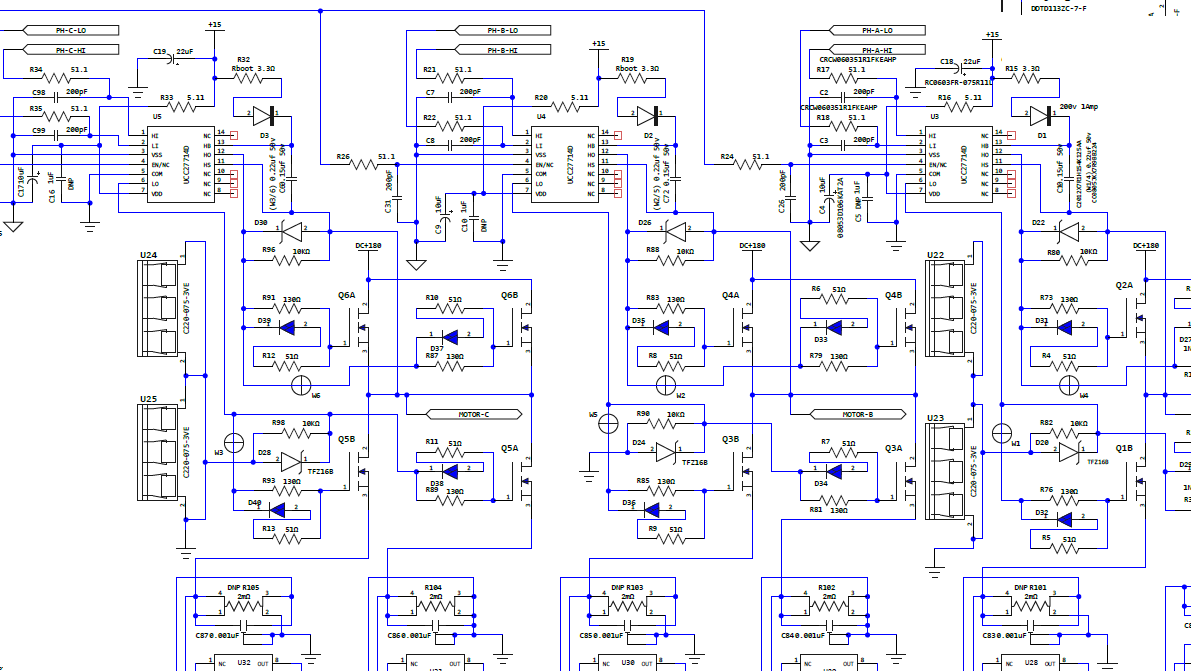

Other Parts Discussed in Thread: UCC27714

您好!

安装新的 UCC 后、我们会检查二极管压降是否与其他安装的 UCC 引脚一致。 奇怪的是,一些新器件 产生1.94v 压降 HO-HS 和 >503mV (HS-HO)。 1.94v 压降仅发生 在中央栅极驱动 器16V 齐纳二极管通过在 HS-HO 引脚上放置10kR 的方式读取两个并联的方法。 移除齐纳二极管测试正常使用新的仍 具有1.94v 压降单向503mV 压降反向探头的齐纳二极管测试将其替换。 在两个 UCC 发生故障后、为了进行良好测量、更换 HO NFET 后也是如此、读数错误1.34v 下降 相同方向1.94v 仅 在中央栅极驱动器上工作 UCC 的下降。 奇怪的 是、1.94v 压降不是 电路外的任何 UCC 上的典型值 HS-HO 压降仅在一个方向上。 然而、一些已知的不良 UCC 会以 1.34v 方式 将探针压降 到引脚上、使其脱离电路。 不要忘记使用 齐纳二极管(HS/HO) 1.94压降 中心 UCC、典型值为0.7V 压降 仅单向。 已检查 PCB 是否存在焊球短路、 尽管 三相换向在 HS/HO 发生短路之前的一段时间内成功、但不存在任何短路。

当其他两个 UCC 不连接、 三个相同的电路未连接电感负载时、如何才能使 UCC HS/HO 在两个方向上都具有压降?

此器件是否可能存在一些通过 QC 的生产问题?