主题中讨论的其他器件: TIDA-00778

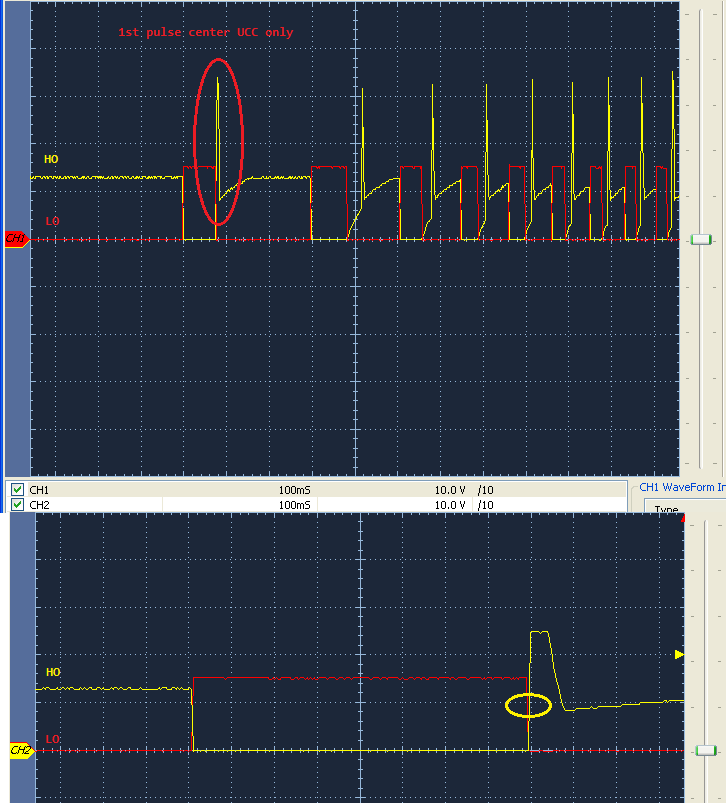

三相电机12.5kHz PWM 换向100Vdc 会导致 HS/HO 结随机故障、没有 通过软 启动/关闭补偿电阻器出现过冲/过冲 HO 的迹象。

使用软 甚至硬 NFET 导通的方法 最终 会损坏 HO 图腾柱、 对 HS/HO 内部 NFET 造成应力。 这样会导致 VDD 电源泄漏到1/2电桥电感器上、从而将 典型的12.6V 浮动偏置电压提升到接近14.3V、例如 通过 HS/HO 击穿导致的 HB 泄漏。

条件:80uS 重叠 PWM 驱动信号 HI/LI 输入、 LO/HO:130欧姆 GTON、 24欧姆 GTOFF (并行 R/肖 特基)、 NFET Qg=<96NC @VBPIN=13.6V

对比度:其他供应商的600V 栅极驱动器(IGPK +/-600/350mA PW<10us) 从未发生过 类似所述的泄漏、 因此需要进行不必要 的芯片更换。

1.维持 IGPK +/-4安培(PW<10us)如何通过 130欧姆 GTon 24欧姆 GToff 电阻器引起 HO/HS 应力?

2. 为了阻止 HS 到 HO 反向泄漏路径首先形成典型 HS 引脚 R 值、需要采取哪些措施?

3、为什么 HO/HS 漏电路径 故障会导致不受控制的超高电感电压过冲?

4.齐纳二极管(15.2VzMin、16.4VzMax @10mA)或在 HS/HO 上放置10k 保护电阻器、 调节浮动 VB 原因是什么?

5. 是否有 Wiki 报告 更新了如何纠正 由行业典型配置引起的 HO 侧栅极驱动故障?