主题中讨论的其他器件: UCC5310

大家好、TI 是否生产了具有负关断功能的栅极驱动器 IC、而无需负电源轨? 如果可能、我宁愿避免使用栅极驱动变压器、那么可能是使用某种电荷泵的器件?

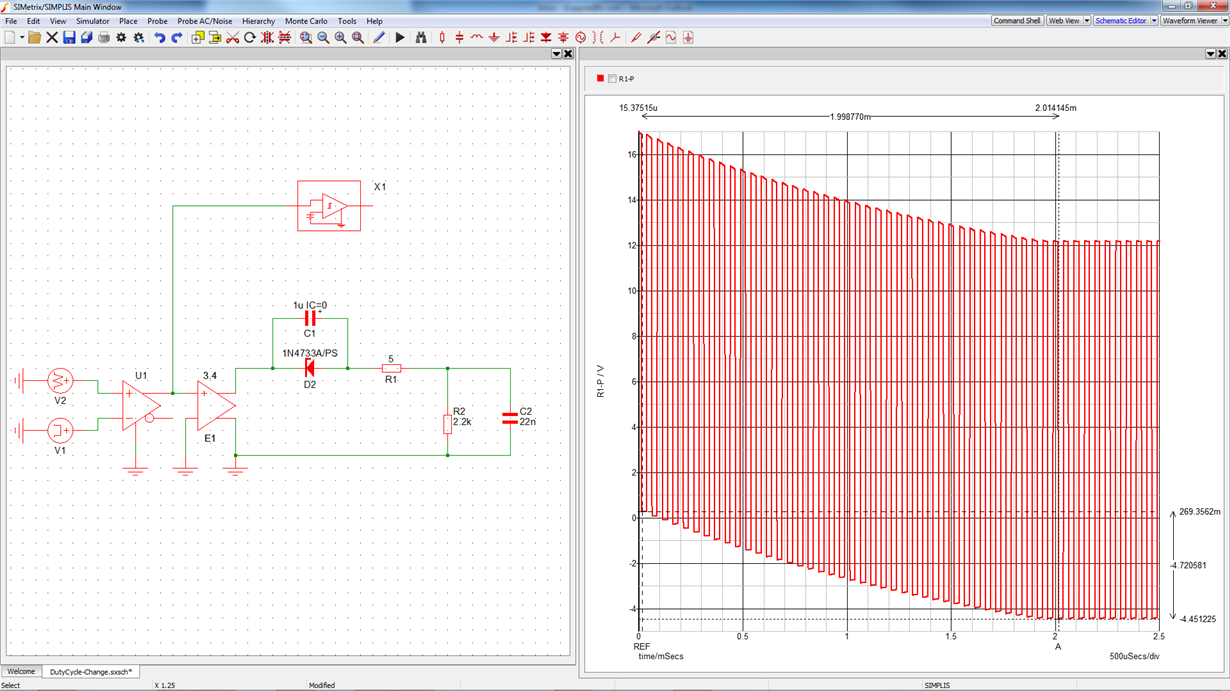

我问、由于在反激式电源中将 FET 重新导通的电容耦合有问题、尖峰是 由 sihg73n60e MOSFET 的漏极到栅极电容引起的。 栅极驱动电压为12v、栅极上的短尖峰仅为几伏特最大值、但该 FET 的导通阈值为2V 最小值、因此它确实会导致它稍微重新导通、 我在栅极上有一个2.2k 下拉电阻器和18V 齐纳二极管、但这不起作用、因为尖峰相对于源极引脚是正的。 在12欧姆栅极电阻器上放置一个关断二极管可以解决该问题、但会因 dv/dt 而导致其他问题。

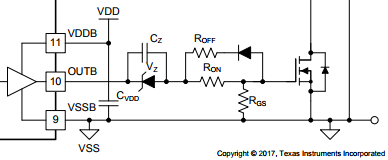

因此、我认为+/-栅极驱动可能是正确的选择、因为我不能通过二极管或其他低阻抗放电路径使栅极关断过快、 在关断时变为负将允许漏极到栅极电容耦合仍然发生、但由于栅极将为负、因此不允许 FET 重新导通、

TI 是否生产出这样一个器件、该器件可能位于 UCC28C45和 MOSFET 之间? 它需要以某种方式从单个12v 轨产生负电压摆幅、并且能够以20kHz 的频率运行、非隔离式良好、N 沟道 FET 位于低侧。

谢谢。