请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

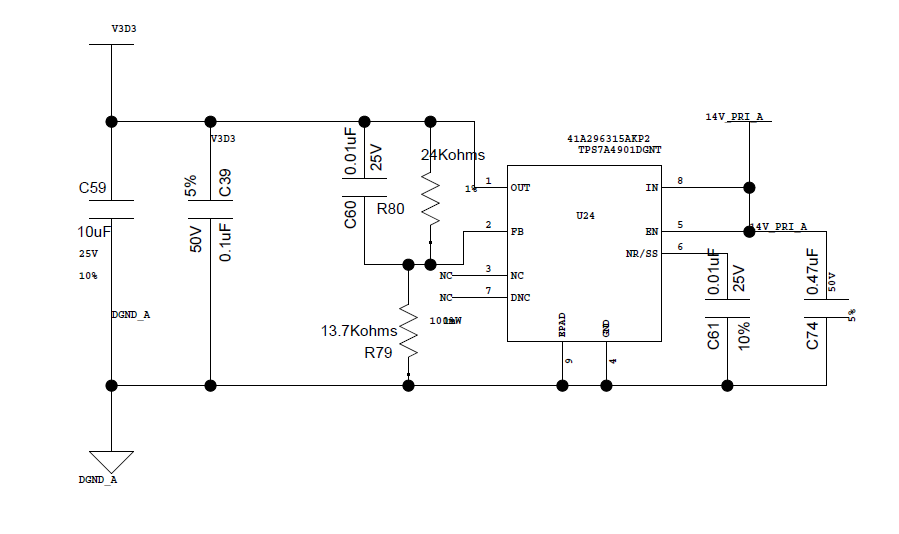

器件型号:TPS7A49 我的客户 正在设计中使用三个 TPS7A4901器件。 其中两个设置为10V 输出、另一个设置为3.3V。 10V 输出没有问题。 但它们在3.3V 输出方面存在一些问题。 对于空载、输出大约为9.7V、而不是3.3V。 它在开环条件下工作。

但是 、当它们放置一些虚拟负载、例如13.7K 欧姆@3.3V 输出时、输出为6.8V。 将虚拟负载增加到1KOhm、我们可以获得3.3V 输出。

使用分压电阻时不应存在最小负载(请参阅所附的原理图)、对吧?

这里还会发生什么情况?

顺便说一下、我让他们把 Cin 增加到2.2 μ F、没有改善。

谢谢!