主题中讨论的其他器件: CSD18543Q3A

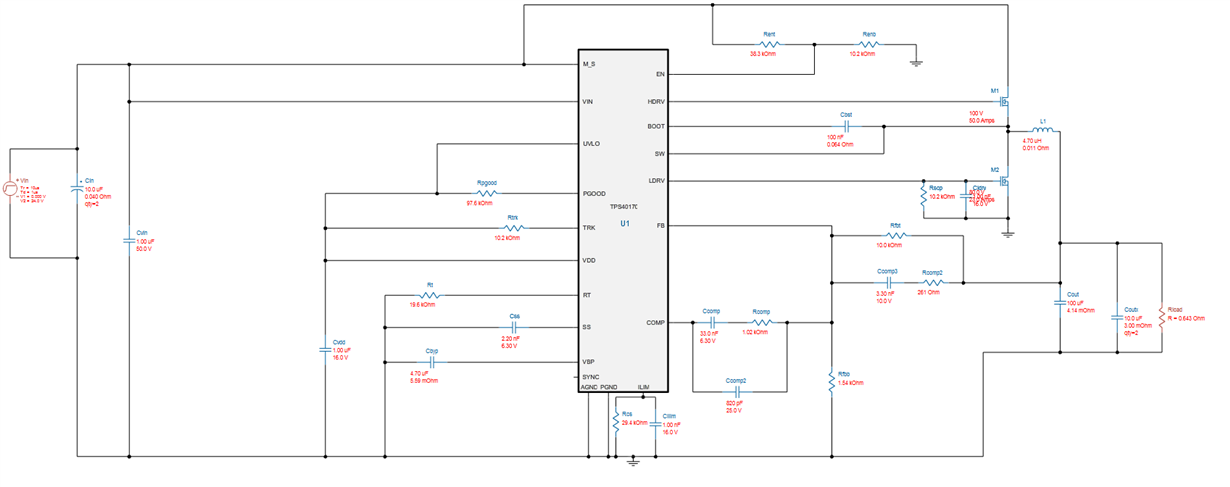

我使用的是 TPS40170。 我是在 webench 中设计的。 输入电压为10-36V、最大7A 时的输出为4.5V

我已启动并运行我的设计。 最初、我遇到了高侧 MOSFET 栅极上的开关噪声问题、导致在特定输入电压下偶尔出现短路(因为两个 MOSFET 都导通)。 但是、输入电源轨上靠近高侧 MOSFET 的一些超低值陶瓷电容器通过消除噪声来解决此问题。

现在似乎一切正常、但我的低侧 FET 变得很热。 12V 时约为90*C,24V 时约为110*C 是我的电路图。 我运行过的热仿真显示低侧 FET 的温度要低得多(最高80*C -无风扇)。

低侧 FET = BSC340N08NS3-G

高侧 FET = CSD18543Q3A

我可以使用一些输入来了解需要注意哪些方面来降低我的温度。 我必须增加 Rlimit 电容器、因为在6.5A 时、由于低侧 FET 中的温度升高、它开始限制自身。