主题中讨论的其他器件: TPS53355

您好!

我正在设计一个使用 lm3150为 CPU 内核生成1.0V 12A (从12V 开始)的设计。 这种情况下可以正常工作、但是 CPU 具有电压调节控制、该控制通过电阻器连接到器件的 FB 引脚。 CPU 供应商告诉我、一旦直流/直流的单位增益带宽在15-300kHz 范围内、这应该起作用。 我找不到此器件的此信息-您能提供帮助吗?

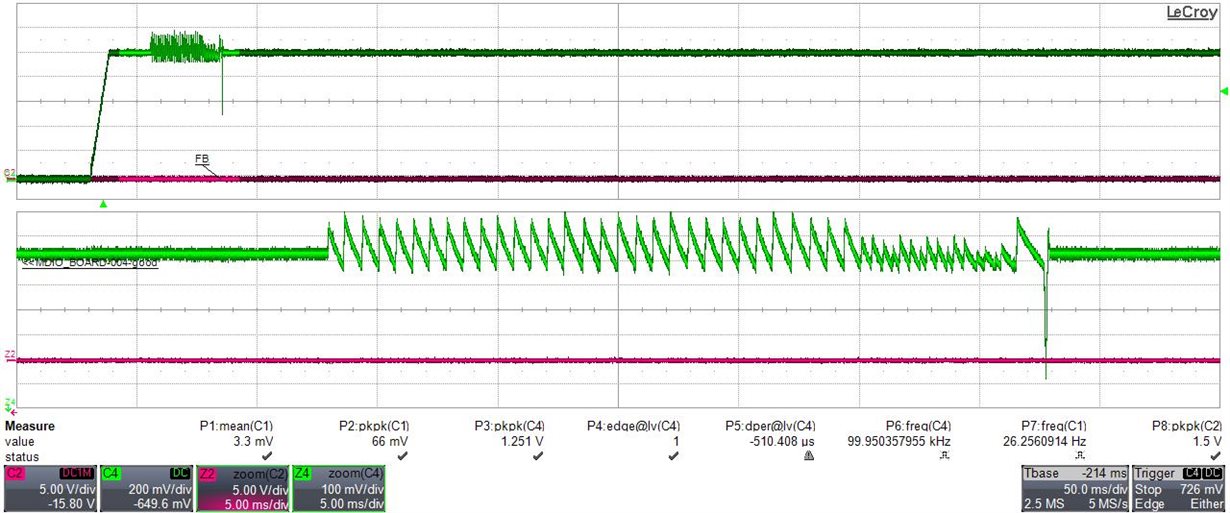

我发现1.0V 可扩展至1.6V、这不应该是这样、所以我尝试进行调试、它显然与 CPU 的反馈控制有关-您能为上面的查询提供帮助吗?