请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS7A47 你(们)好。

我已应用 TPS7A4701在电路中实现低噪声电源。 为了实现"3.3V"的输出电压、使用"3.8V"作为输入电源。

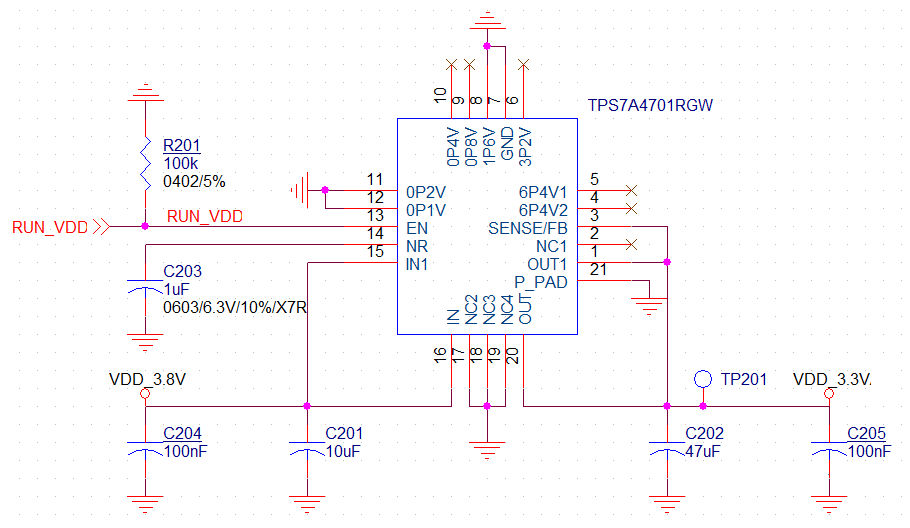

详细电路请参考下图。

为了控制 LDO 输出(开/关)、LDO 的使能引脚与100k Ω 下拉电阻一起分配给 MCU 的 GPIO、

我确认 GPIO 控制已清除。 (状态为3.3V (开)或0V (关)。)

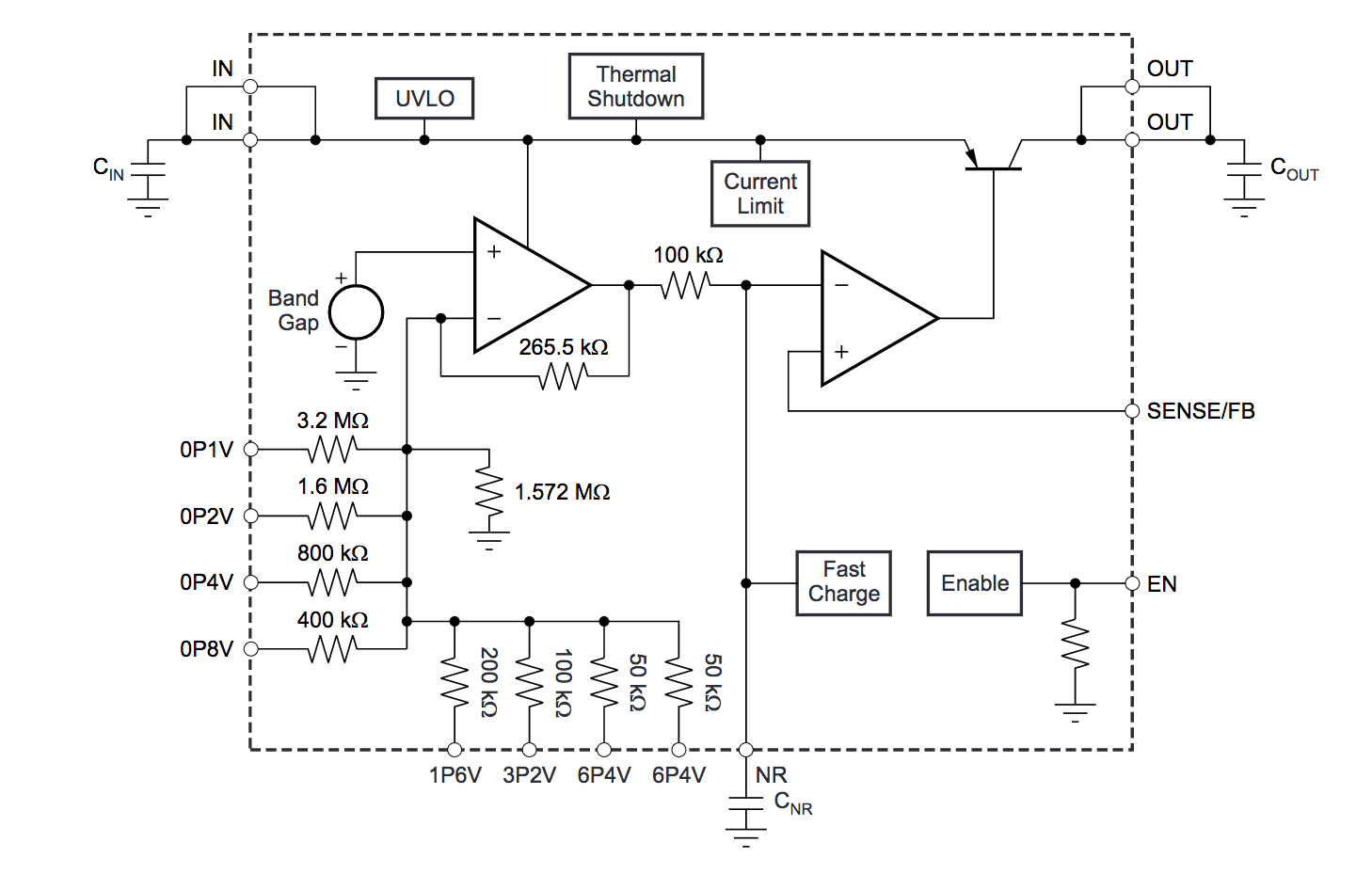

这里的问题是、将 GPIO 设置为"低电平"不会关断 LDO 输出。 (在本例中、输出电压电平为1.3V。)

为了实现正常的关闭操作、请确认要修改的零件。

此致、