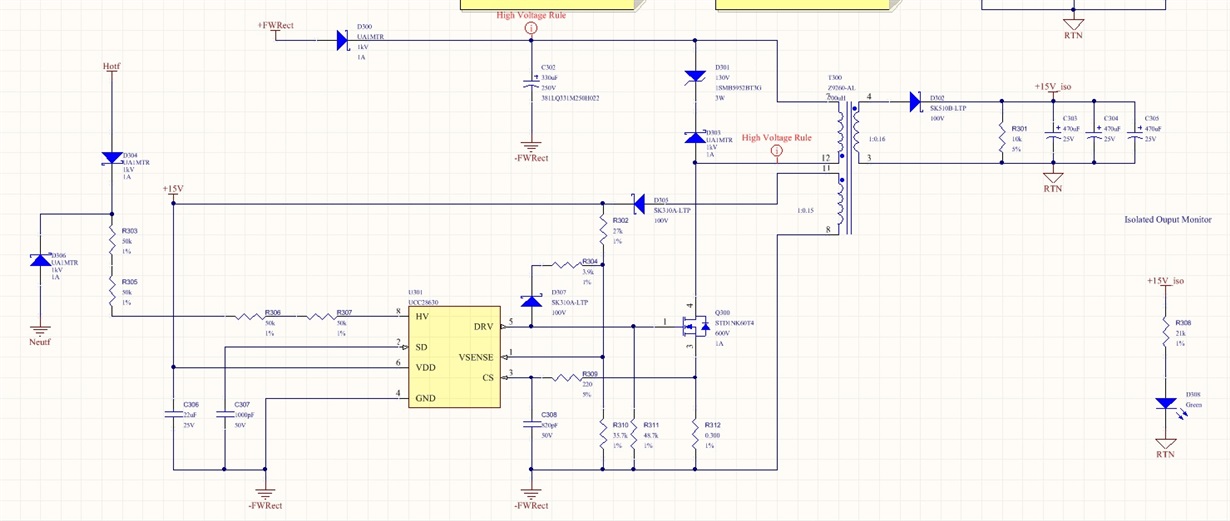

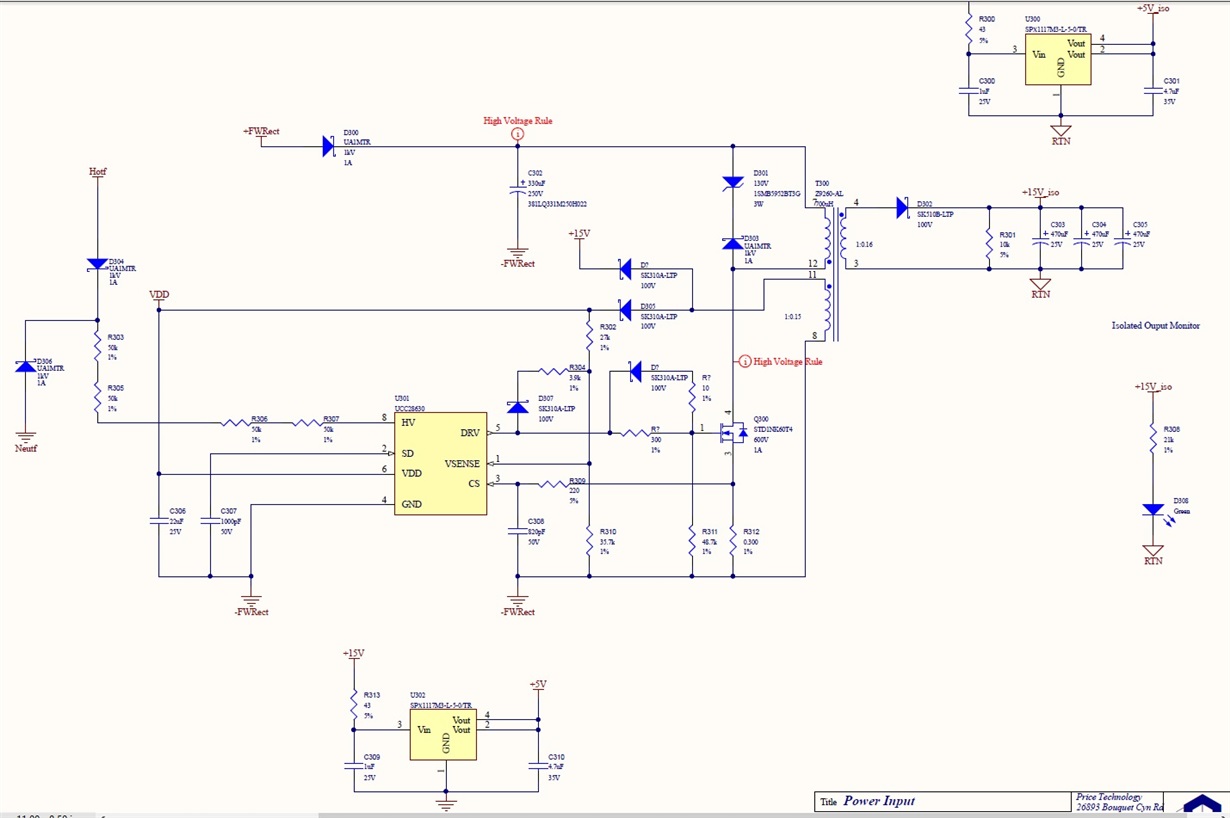

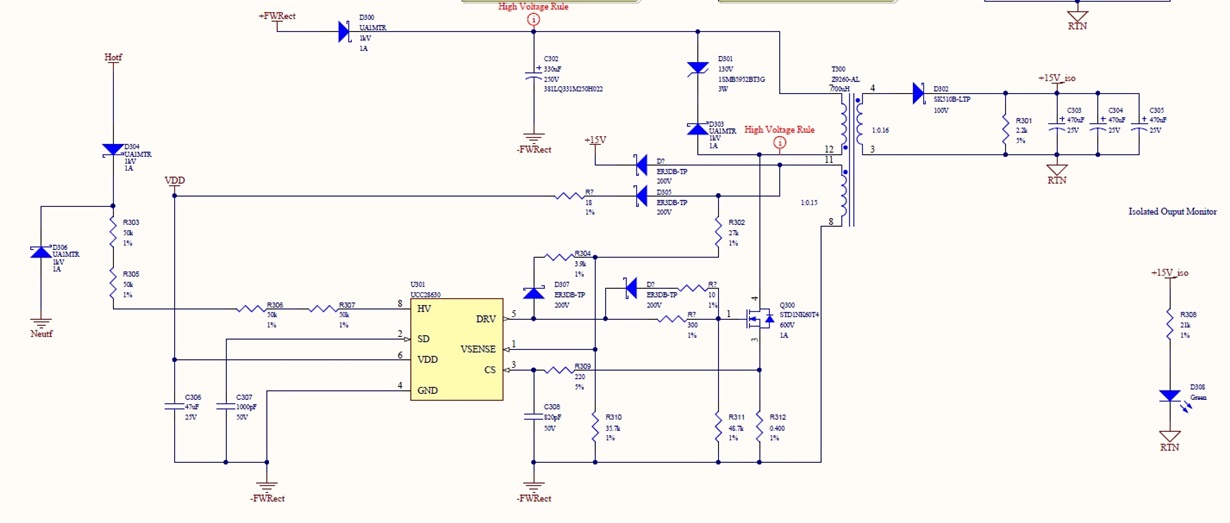

我使用 UCC28630 (定制设计/布局)为新的反激式设计加电。 所有型号和大多数布局均已通过验证。

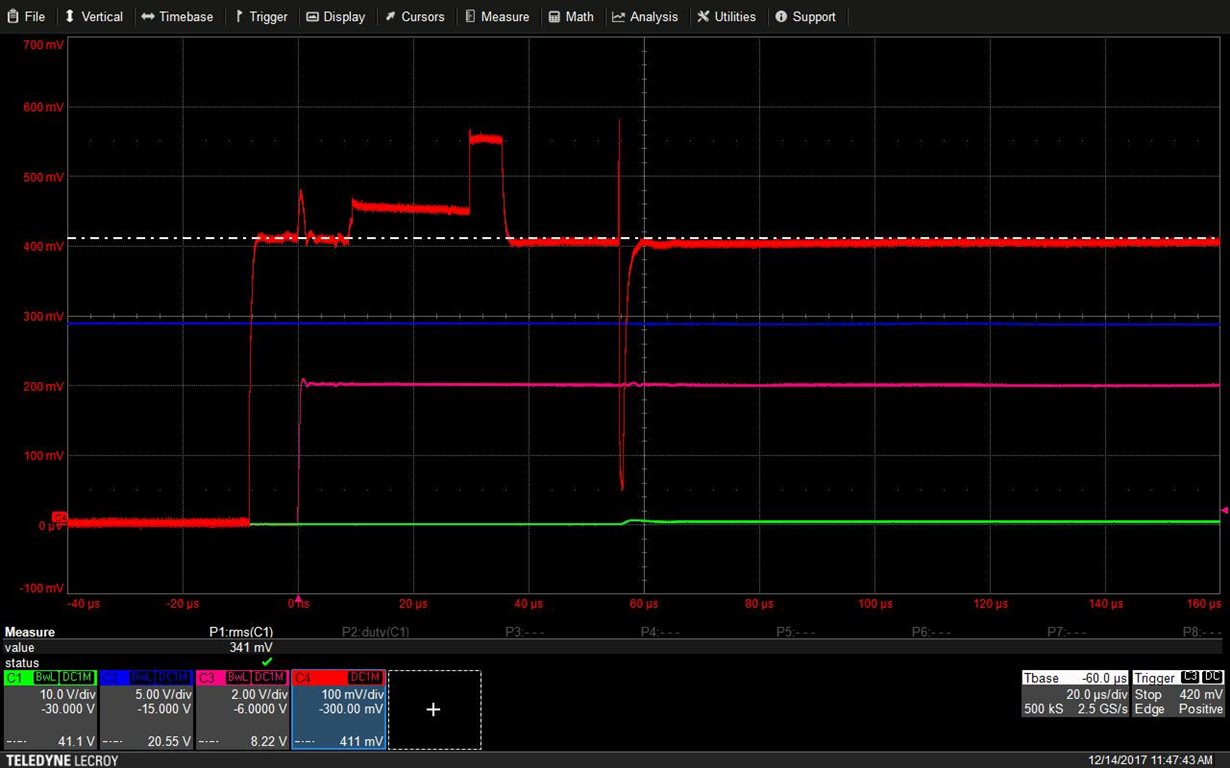

我一直在关注电流问题、因为电路看起来应该正常工作;但是、当从120VAC 供电时、VDD 引脚在8V-10V 之间抖动、就像芯片上锁存了故障一样。 从不存在 DRV PWM 电压、发生锁存故障时 Vsense 引脚的电压读数为5.5V。 观察 SD 引脚时、我会看到30us 脉冲、然后是21x 1us 脉冲。 这告诉我、根据其他人的帖子、我对 Vsense 有开放或简短的看法。

我关闭了电路、移除并测试了电阻器和所有测试、尽管 fb 电路应该正常运行。

导致这种情况的其他原因是什么?

请注意、VDD 上的脉冲序列永远不会达到适当的峰值电压。 它们更像是低振幅脉冲(0.5V)。 该电路现在仅在反激式变压器的次级侧组装了10k 负载。 这会产生问题吗?

反馈电阻为27k、35.7k、初级侧与辅助侧的匝数比为0.16。 如果有必要、我可以发送一大块原理图、尽管我实际上只是在寻找要寻找的地方。