主题中讨论的其他器件:RM41L232、

您好、请告诉我。

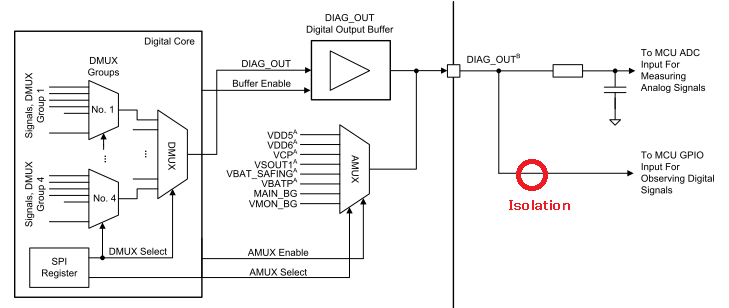

当将 diag_out 同时用作 ADC 和 GPIO 时、它会写入数据表中、如下所示。

如果应用必须使用 MCU ADC 测量模拟信号并使用 MCU GPIO 监控数字信号、请执行

应用设计必须确保 GPIO 输入级不会影响 ADC 测量。 隔离 MCU

在 MCU 中无法实现 GPIO、应用设计必须在外部实现必要的隔离。(数据表:34页)

当两者都使用时、尽管有人说 GPIO 是隔离的、但如果使用电感器、是否没有问题?

此外、请告诉我们 AD 和建议的 R 和 C 常数。