请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LP8860-Q1 尊敬的 TI 专家,

我现在在显示项目中使用 LP8860A-Q1、 但在80M/90m/100MHz~下未通过 EMI 导通测试

您能就此提供任何建议吗?

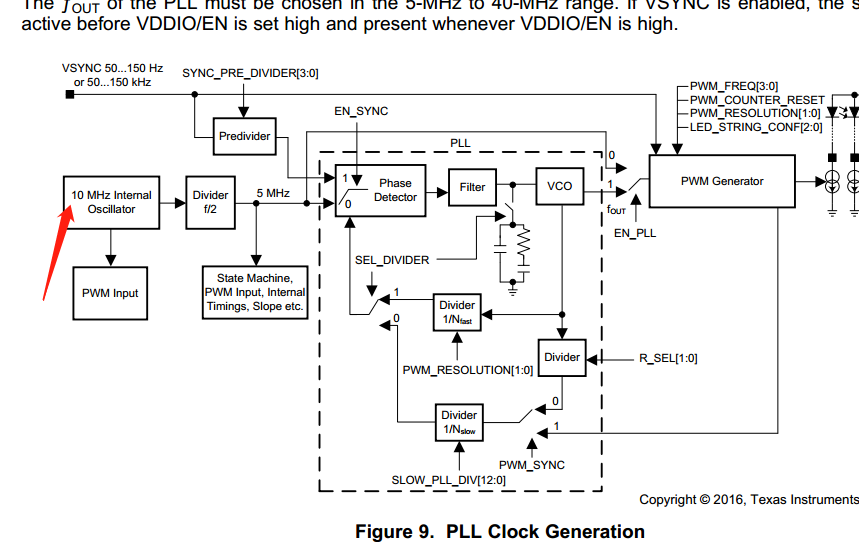

我们使用近场频谱来测试 LP8860、我们确实找到了10MHz 峰值频率及其谐波、并且 VDD 引脚会产生很多~μ s 的频率

我想知道 为什么10MHz 频率耦合到 VDD 引脚?

如数据表中所述、它们是10MHz 内部振荡器。

我将 PLL 接线、这毫无意义。