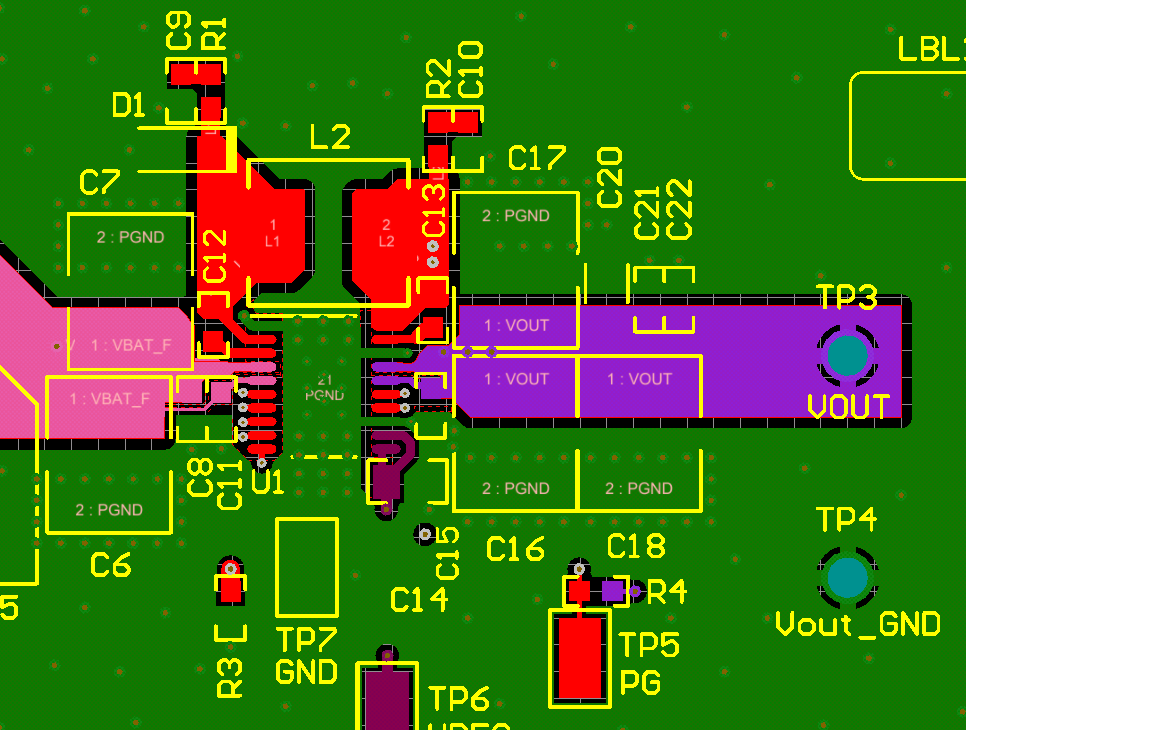

我在 PCB 上安装了 TPS55165。 输入范围为8至18V。 输出电压为12V、 所需电流最大为320mA、典型值为120mA。 双面板、底部是接地层。 根据数据表、所有电容值。 当我打开它时、我会得到3到10伏的输出电压。 有时、我必须在输入电压达到10V 之前上下改变输入电压。 我使用3个陶瓷电容器和2 x 1 uF 将 VREG 上的电容器增加到了6.8uF。 输出 C 为2 x 22uF、具有.01和.1uF。 输入 C 为2x2.2uF、15uF 钽电容器、0.1和.01uF 电容器。 IGN 为高电平、PS 和 IGN_PWRL 为低电平。 PG_DLY 接地(尝试连接到 VREG、无变化)。 有时上电时 PG 为高电平(100K 至+5上拉)、有时保持低电平。 布局与所示的布局类似、所有布局都非常紧凑、并具有接地层。

底线是、在任何情况下、我都无法使它输出12V 电压。 是否有任何关于要检查的内容的想法? 如果不是、我将尝试一些不同的器件、因为我不能在生产环境中冒险这种挑剔的事情。

数据表不是我从 TI 看到过的最好的数据表。 我不确定 IGN_PWRL 被称为"锁存器"意味着什么。 我将介绍数据表中的第8.4.3节和图16、这意味着您只需上拉 IGN (我具有1K 至+5)并将 PS 和 IGN_PWRL 接地。 我只希望它打开并在加电时保持打开(无低功耗)。 无论我使用什么、我都会首先切割测试板(这是整个系统的第一个原型)。 它实际上应该像放置在无源器件上并输出12V 电压一样简单。