请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS659039-Q1 大家好、

我的客户对 tps659039的电源序列有一些疑问、请帮助检查:

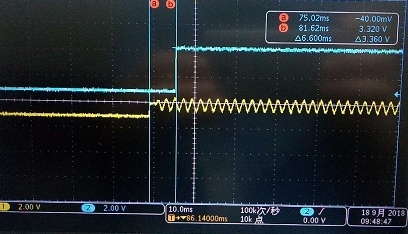

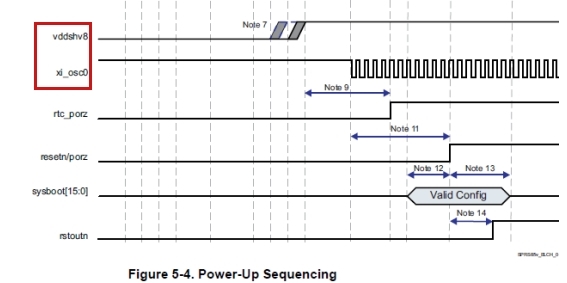

xi-osc0比 vddshv8提前6.6ms 上电、这与所需的电源序列不同? 是否存在风险以及如何改进?

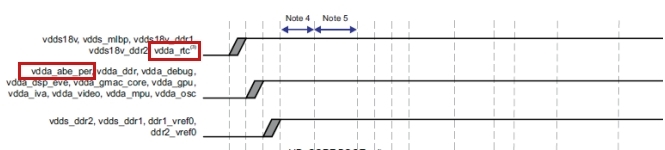

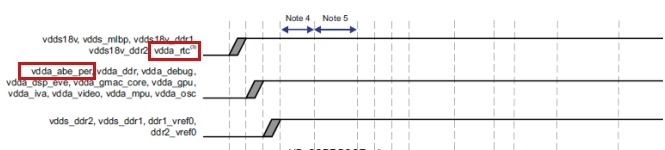

2.与 VDDA-RTC 和 VDDA-Abe-PER 类似的问题是,实际测试显示 VDDA-Abe-PER 比 VDDA-RTC 早0.58ms。

OTP 版本为 O9039A387IZWSRQ1。 谢谢

东宝