尊敬的所有人:

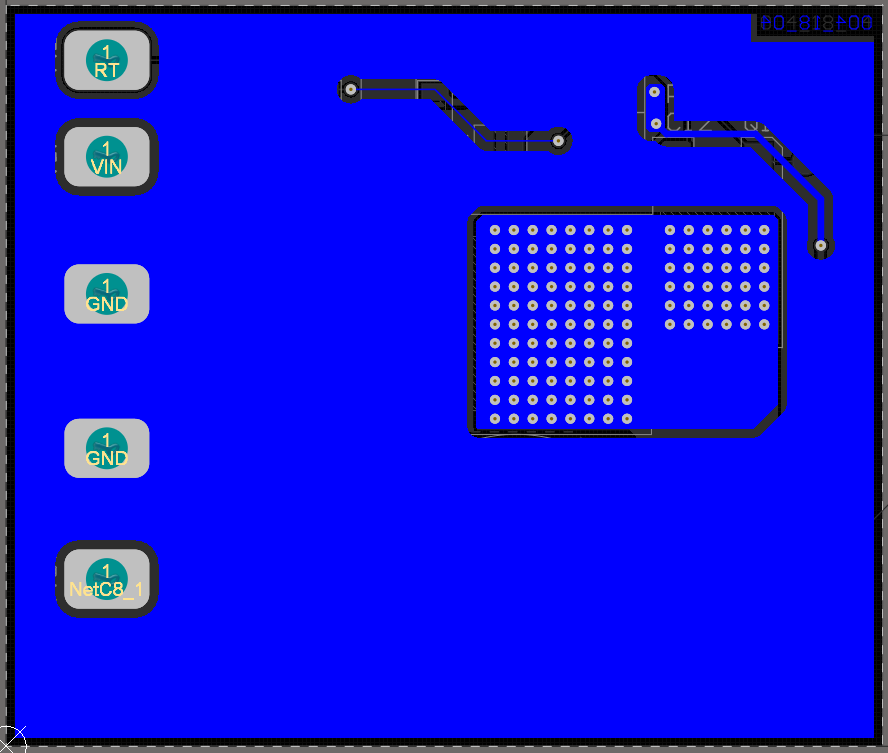

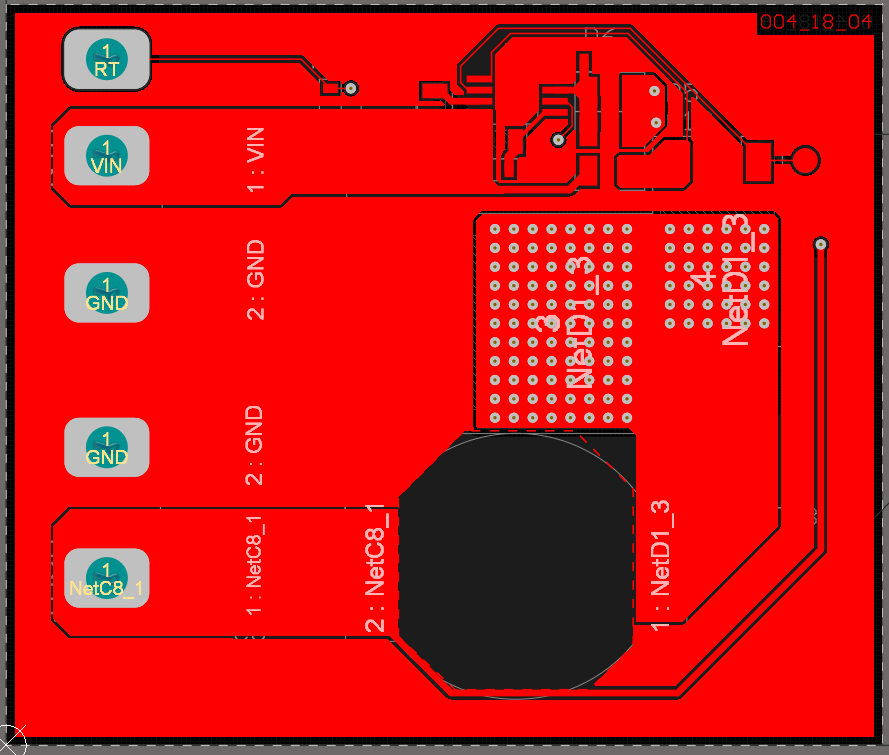

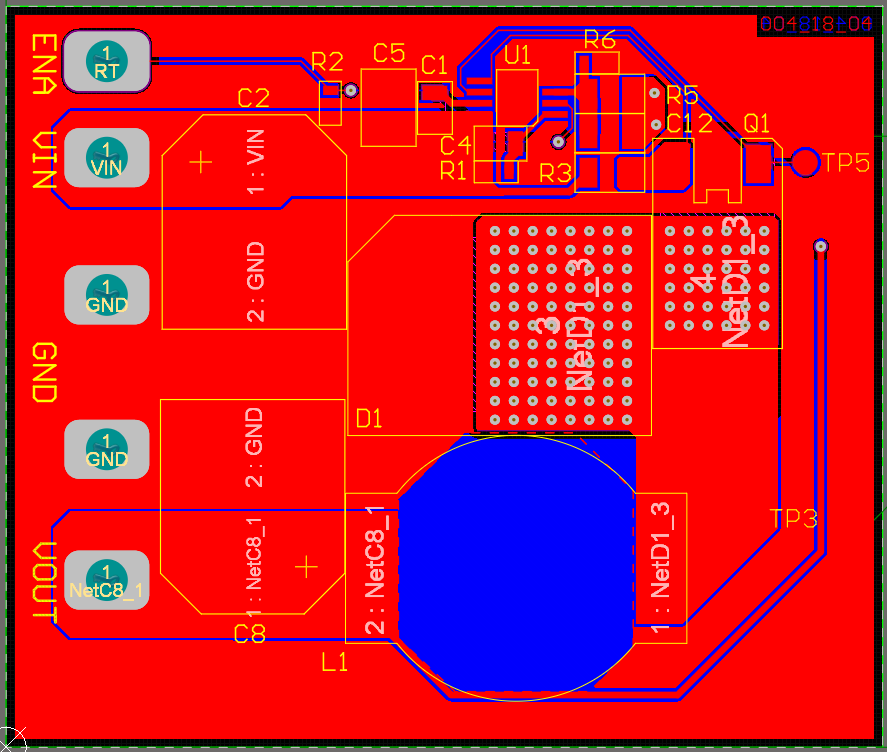

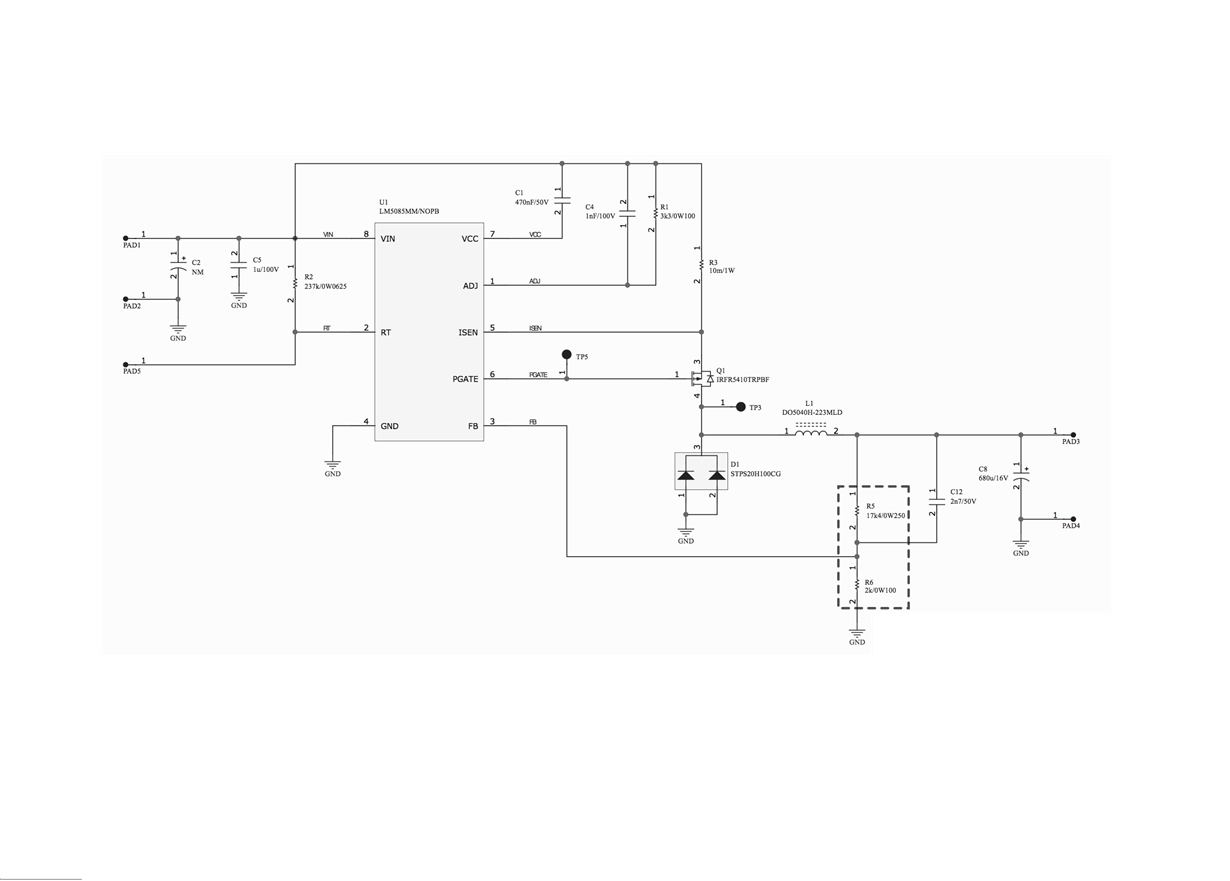

在我的最后一篇文章中:LM508不适用于35Vdc 以下的 V_input。当 IOUT 大于5A 时、我遇到了 EMIS 问题。 我修改了布局、将控制器移到远离 SW 节点的位置、同时尽可能减小了 SW 节点的面积。

通过这样做、我实现了在输出时能够达到7A。 但是、对于较高的值、当 直流负载配置为10A 时、直流/直流开始工作时、PWM 频率衰减高达20-30kHz、VOUT 为0.72V、输出电流为6.5A。 我真的相信、我会遇到 EMIS 问题、我已经完成了布局。

我计划将层数增加到4层、并将 GND 过孔放置在靠近 PCB 边缘的位置、您认为两者都足以大幅降低 EMIS 吗?

非常感谢!

David