请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS54394 大家好、

我的客户在其项目中使用 TPS54394来为 FPGA 加电。 他们希望使用电源正常引脚和 EN 引脚来实现加电序列管理。

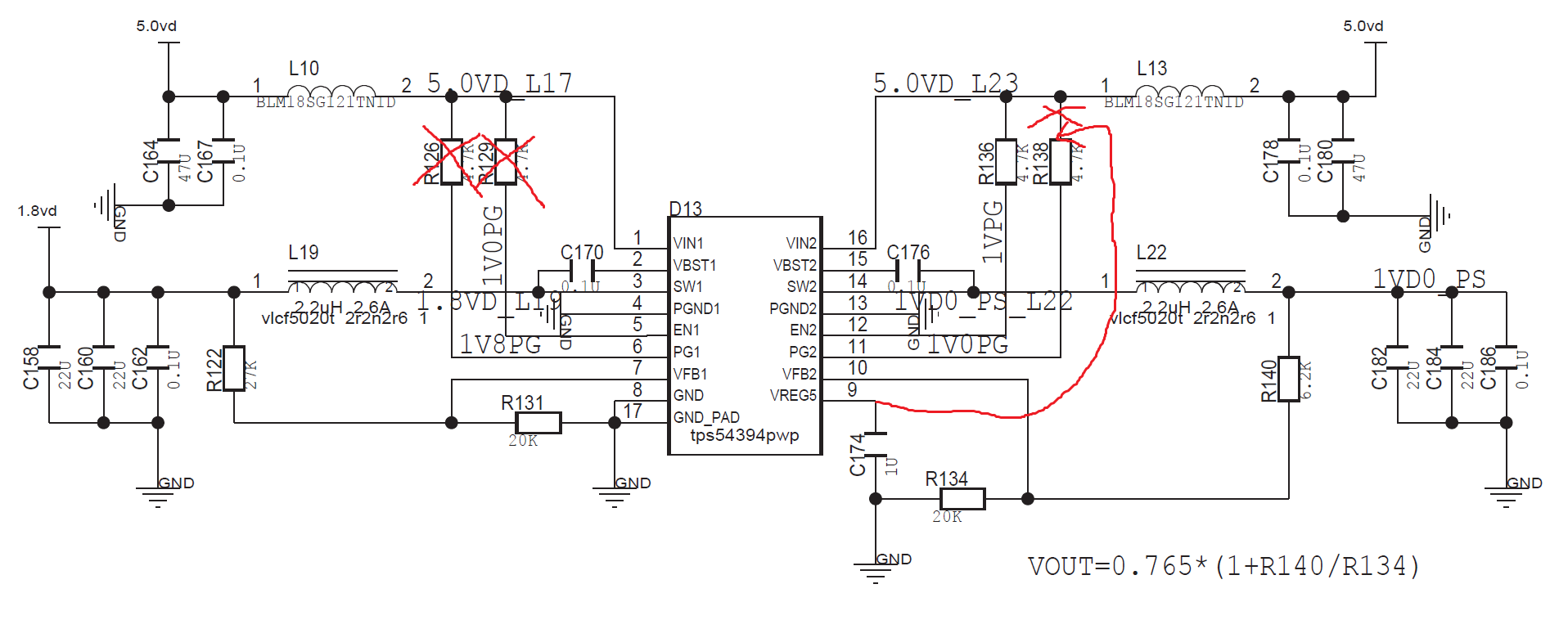

原理图如下所示。 红线是一些调试更改。

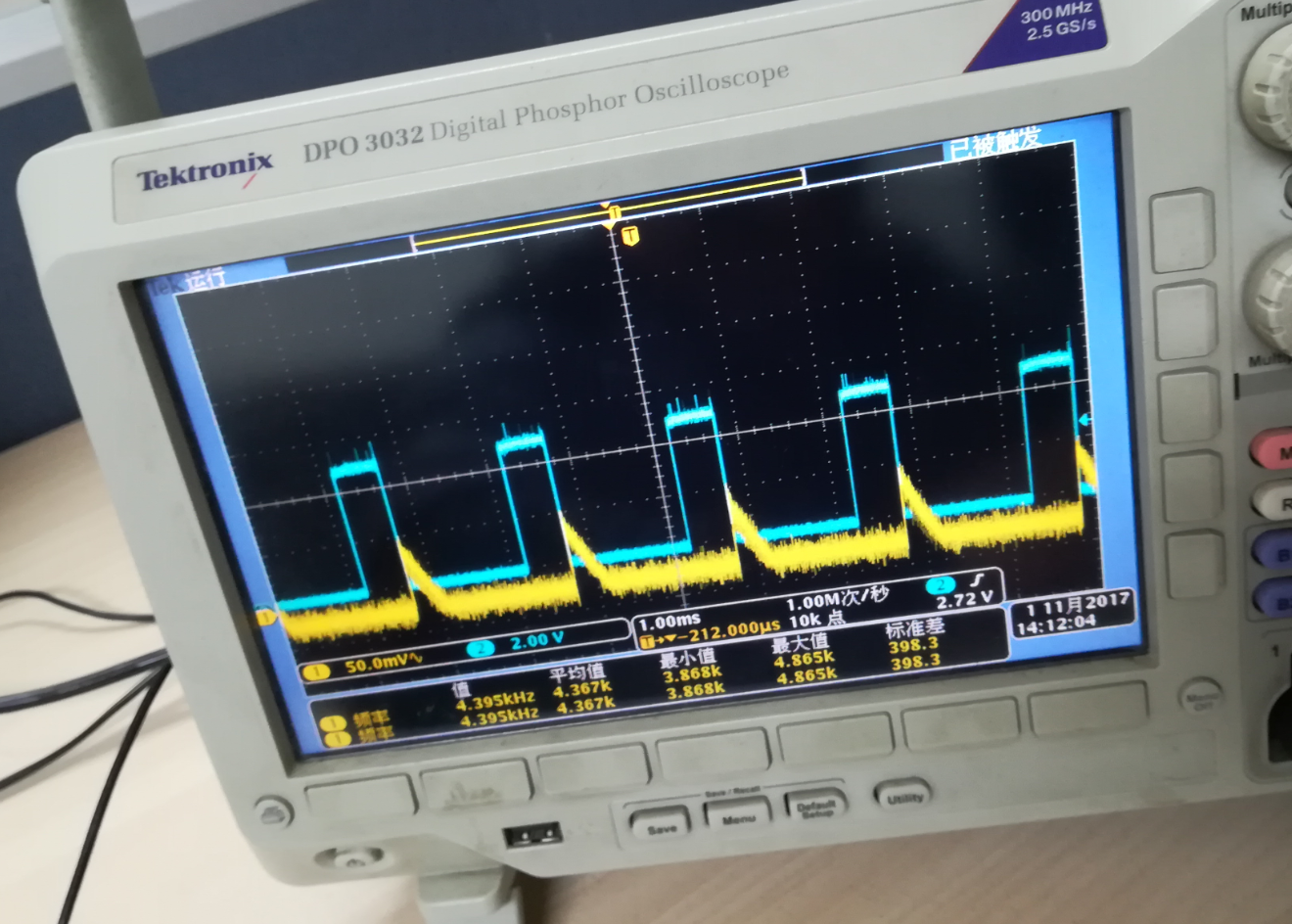

输入 电压为5V、Vout1为1.8V、Vout2为1V。 使用 PG2控制 EN1、移除了 R129。 PG2通过4.7K 电阻上拉至 VREG5。 Pg1左浮动、R126旋转。 但输出 异常。 PG2 (Bule)和 Vout 交流耦合纹波(黄色)、如图2所示。 电源正常现在不好。

如果我断开 PG2与 EN1的连接、并通过4.7K 电阻器将 EN1上拉、则输出电压没有纹波、PG2输出高电平。

我不知道这种分裂有什么错误。 可以发表一些意见吗? 我们应该如何使用电源正常引脚和 EN 引脚 为 TPS54394中的序列管理加电?

图1.

图2.