主题中讨论的其他器件: UCD90SEQ64EVM-650、 SEGGER

使用 UcD90120A 时、我们的一些电路板出现问题:

在100块电路板中的6块电路板上出现问题。 其余94块板工作正常

6个电路板中的5个是新生产的、但其中6个是我用于在 UcD90120A 上获取配置的板。

在第6块板上、JTAG 重新编程配置后出现问题。

我们使用 JTAG 对板进行编程。

我们使用的是400kHz 的 I2C。 上拉电阻为1k Ω。

ADDR 电阻器均为90.9k Ω、I2C 地址为0x68。

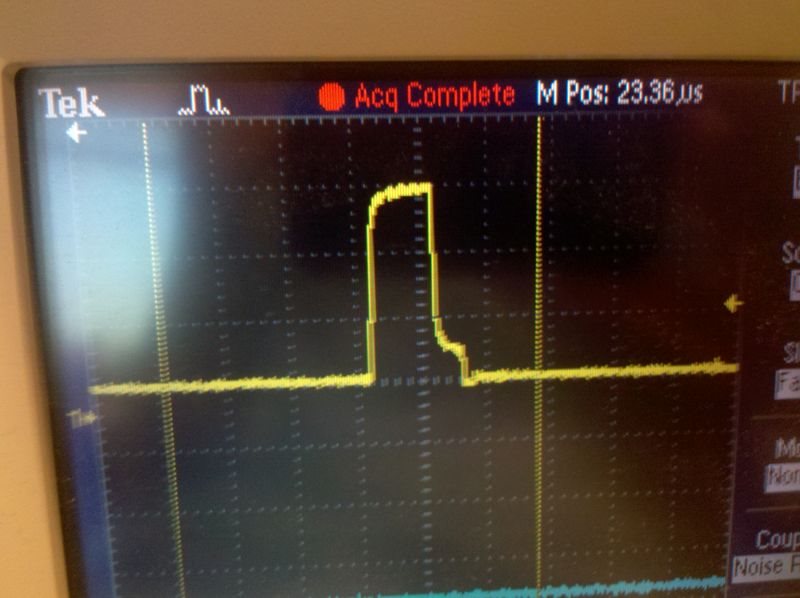

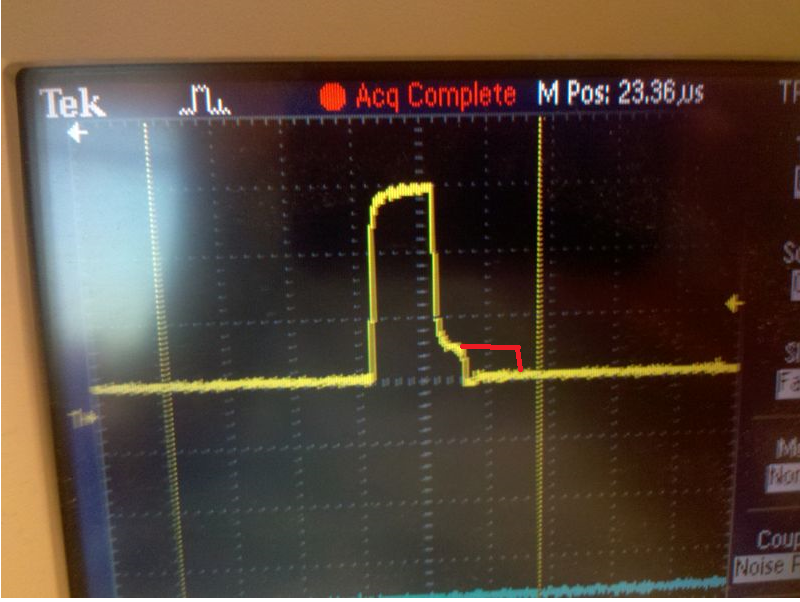

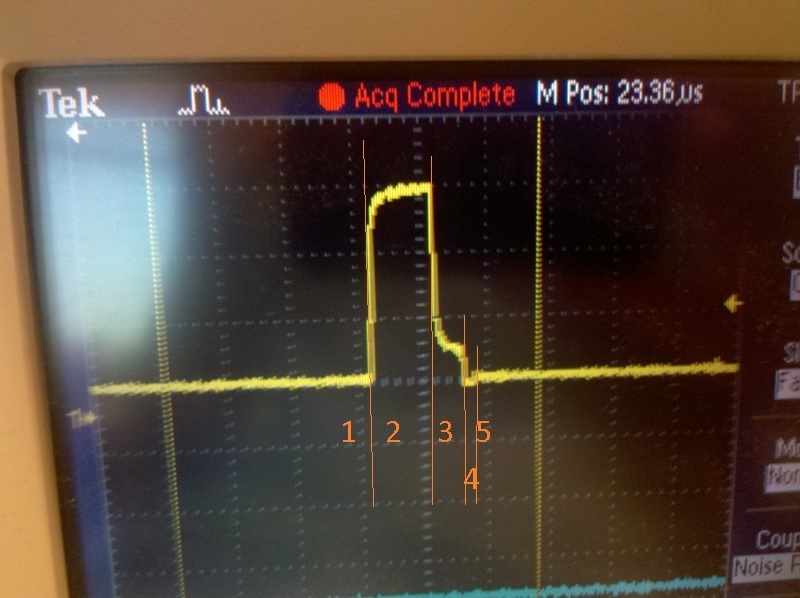

从 SCL/SDA 的范围内可以看到、SCL 在访问的第9个上升沿(在 ACK/NACK 的中间)之后(0.2us)被 UcD90120A 拉低、而不管 I2C 总线上发送的地址如何。

我可以看到、SCL 首先被 UcD90120A 拉低、然后由 I2C 控制器拉低50ns、并在 I2C 控制器继续生成400kHz 时钟脉冲之前保持低电平1.25us。

有什么想法我可以做什么来修复这些板?

我尝试通过 JTAG 重新编程固件、但这不能解决问题。

此致、

Søren M.

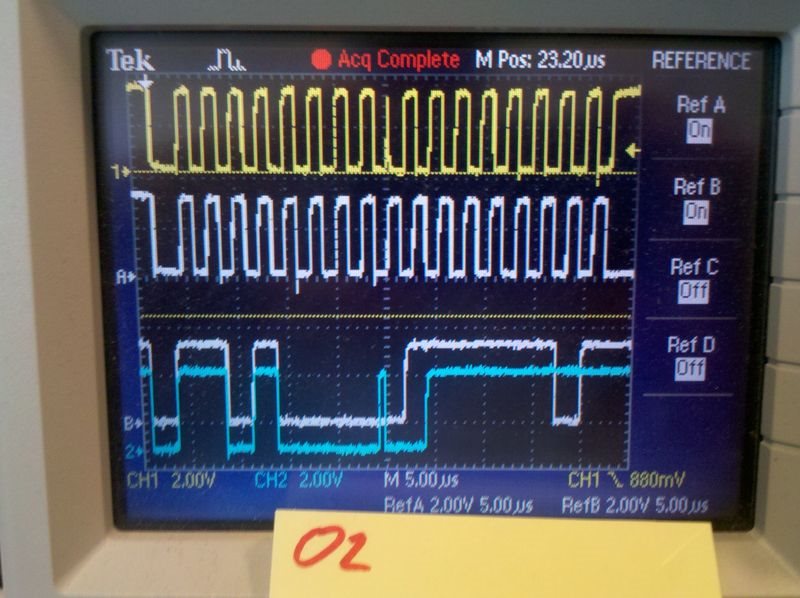

示波器屏幕截图:(黄色:SCL、蓝色:SDA、白色:工作板参考)