降级器、

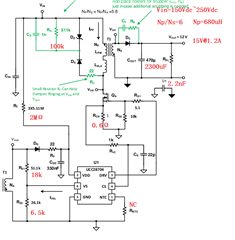

客户反馈、当他们使用 UCC28704 反激式电源时、输出电压为15V/1.2A、当负载较轻时、输出正常、当负载较重时、输出不稳定。

请帮助检查原理图是否正确。

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Ning、

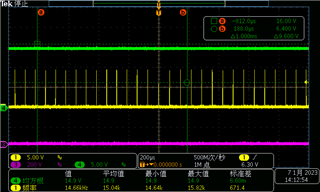

感谢您的联系。 您能否在一张图片中提供输出电压、VDD、栅极(DRV)的波形?

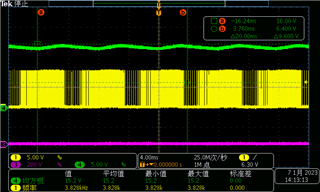

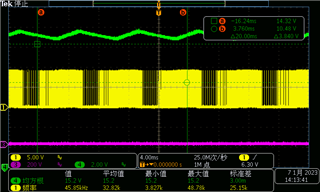

根据您提供的波形、似乎 FET 暂时停止开关、因此输出下降。 当 VDD 降至 UVLO 阈值(典型值为7.7V)以下时、会发生这种情况。 如果 VDD 反复下降并触发 UVLO、 则增加 CDD。 (计算可基于 UCC28704 Excel 设计计算器)

您还可以提供辅助绕组吗? (Np:Ns:Na)

提前感谢。