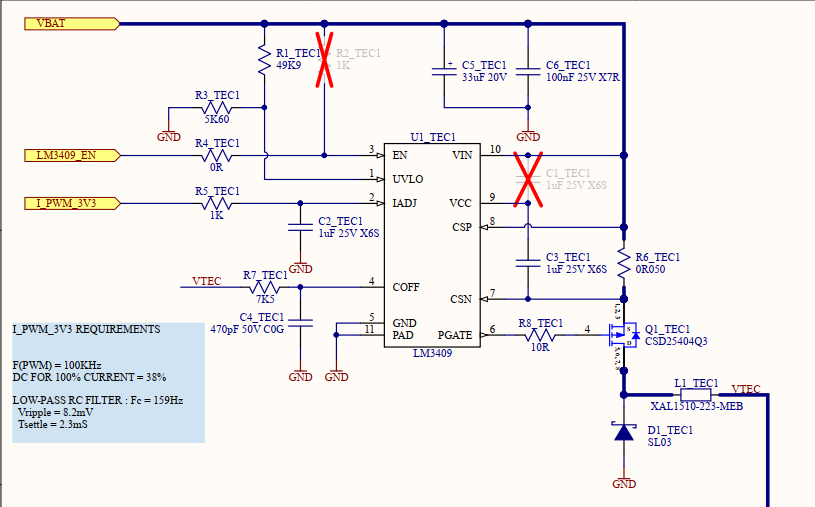

Other Parts Discussed in Thread: LM3409

我使用 LM3409通过50m Ω 感应电阻器驱动最大输出电流设置为约4.85A 的电流控制器件(不是 LED)。 但是、我打算使用 IADJ 引脚动态减小电流、以控制输出器件。 但是现在我只是测试电路,以确保它按预期工作,而不是。

问题在于、当连接输出器 件(使用板载 H 桥或手动完成)时、输出电流立即跳至具有可编程电流限制的实验室工作台电源的限制。 目前、我只使用0.1欧姆10W 功率电阻器来简化操作。

我已对 IADJ 引脚和 EN 引脚进行了范围划分(连接时:深蓝色为 IADJ、浅蓝色为 EN)。 我动态控制这两个器件、因为这是目标器件所必需的。 您可以看到、我每1.2秒左右就会关闭 LM3409、IADJ 引脚驱动至0V。 然后、开关输出 H 桥、再次启用 LM3409、然后 IADJ 引脚斜升至其最大值(在本例中为~350mV)。 这一切都是为了减少输出电路中的热应力、尽管最终应用的周期将延长大约100倍。 我缩短了测试时间、使测试更轻松、更快速。 该示波器是在移除输出器件时获取的、因此没有负载。 这也证明了我不会得到 H 桥 FET 的死区短路。

我的理解是、当 IADJ = 350mV 时、输出电流应限制为感应电阻设置的最大电流的0.35/1.24。 因此、在本例中、该值为~1.4A。 但当我连接负载时、我看到电源达到电流限制、输出电流高达5A! 因此、由于某种原因、LM3409未观察到电流限制。

我填充了 C3、因为根据数据表第22页的讨论、Q1最初具有大得多的栅极电容。 我还没有更新原理图来解决这一问题、尽管我的理解是、这会导致更多的电感器纹波、这一点现在不太令人担忧。

是否有任何关于正在发生什么或如何调试发生什么的想法?