主题中讨论的其他器件: UCC256303

大家好、

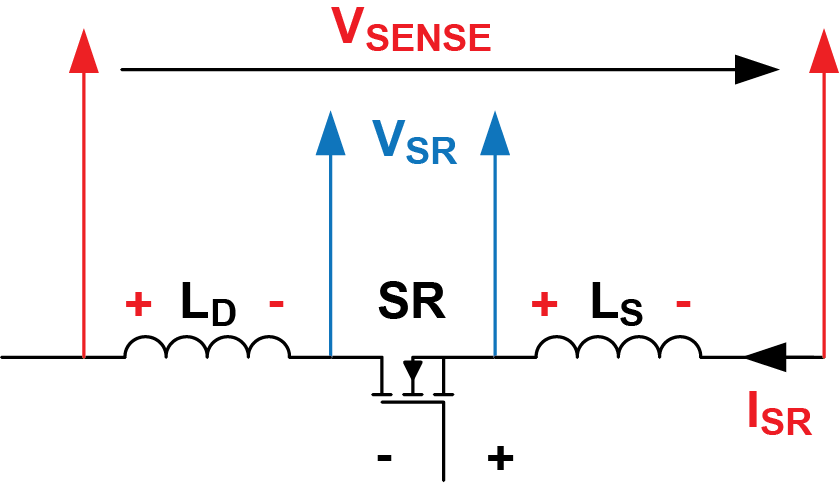

我的客户 将 UCC24612-2连接到了 LLC 电路。 秒 使用辅助导线进行整流。

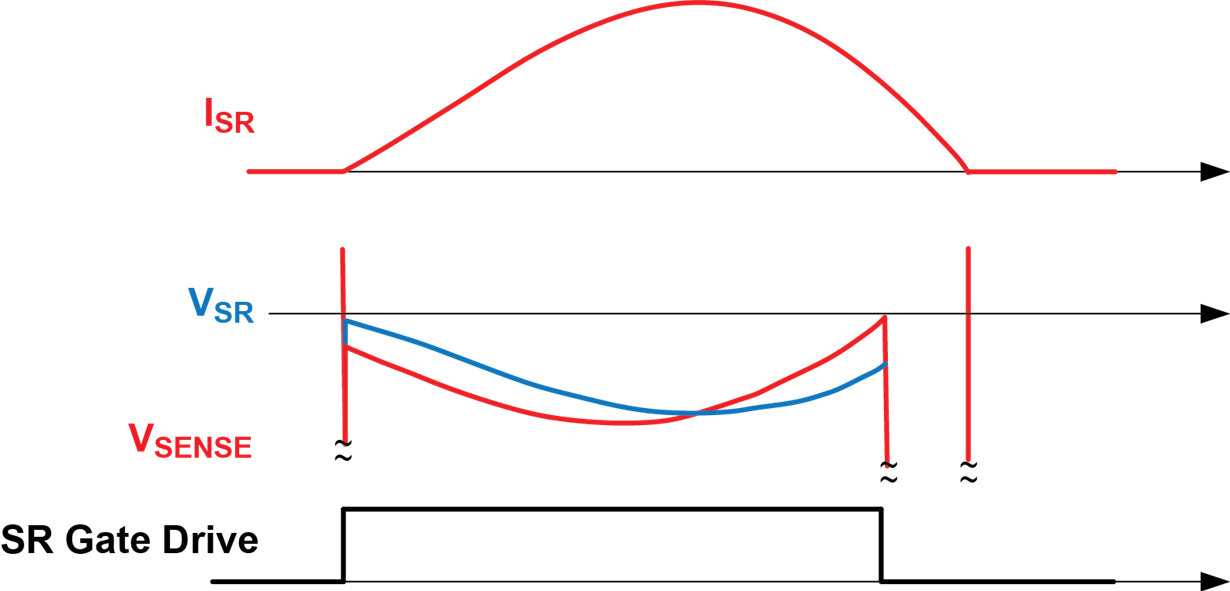

第一个160ns Vgs 为9.5V、下一个电压低至6V。

输出电压为60V、因此使用辅助导线。

但3kW 大功率需要较大的并联 MOSFET、Rdson 为7m Ω、

并需要高 Vgs 来实现较低的 Rdson。

VGS 6V 过低、无法保持 MOSFET 的较低 Rdson。

这会导致效率较低的整流器。

是否有某种方法来保持高效率、从而使高功率 MOSFET 需要高 Vgs。

谢谢你。