Other Parts Discussed in Thread: LM5085

我尝试使用 LM5085来限制通过烧断线的电流和电压、当施加电流时、该器件会在海水中腐蚀。 负载是纯阻性的、但电阻会因水温、盐度和其他因素而变化。 此应用与 CC/CV 电池充电器非常相似。

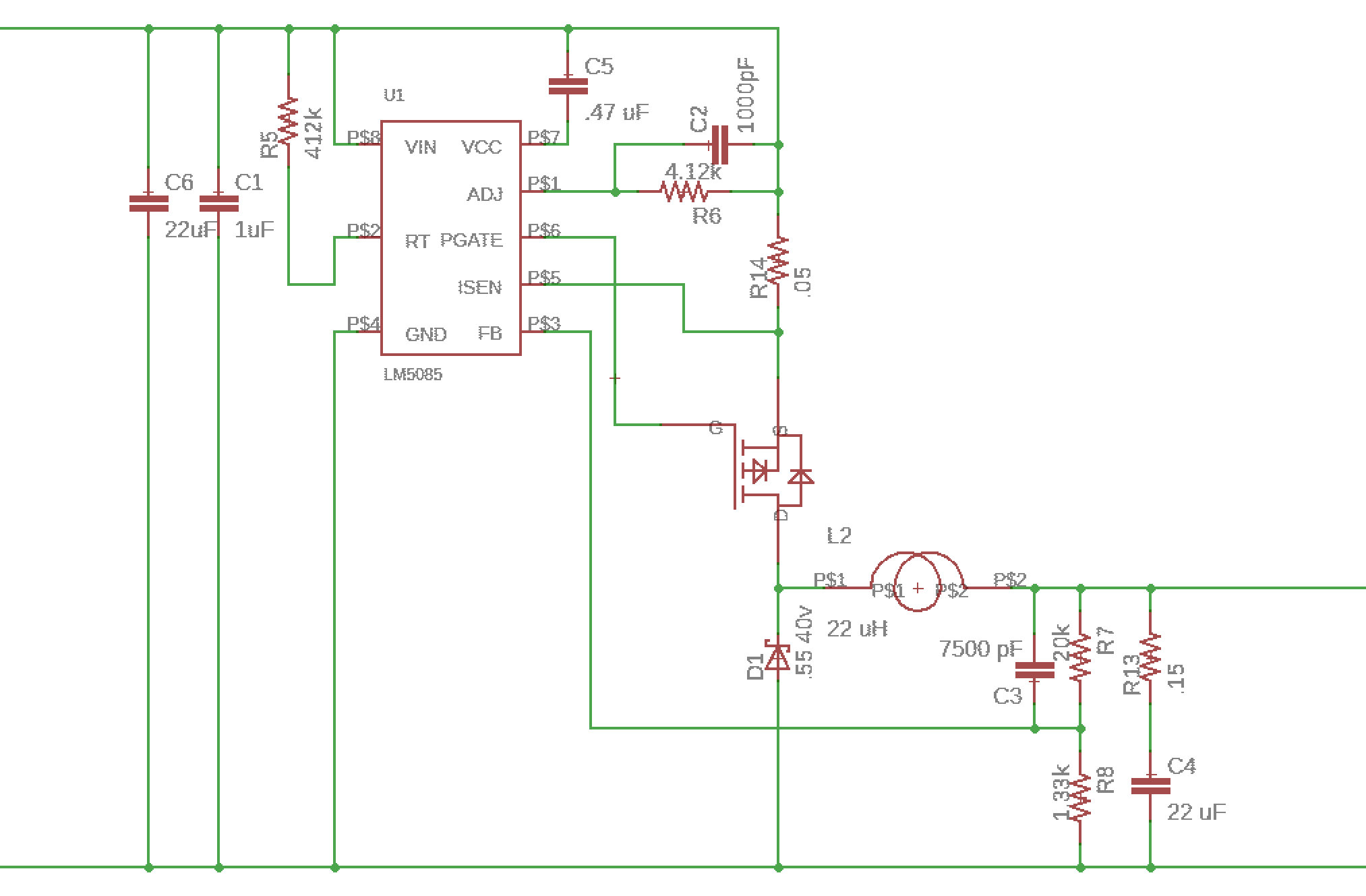

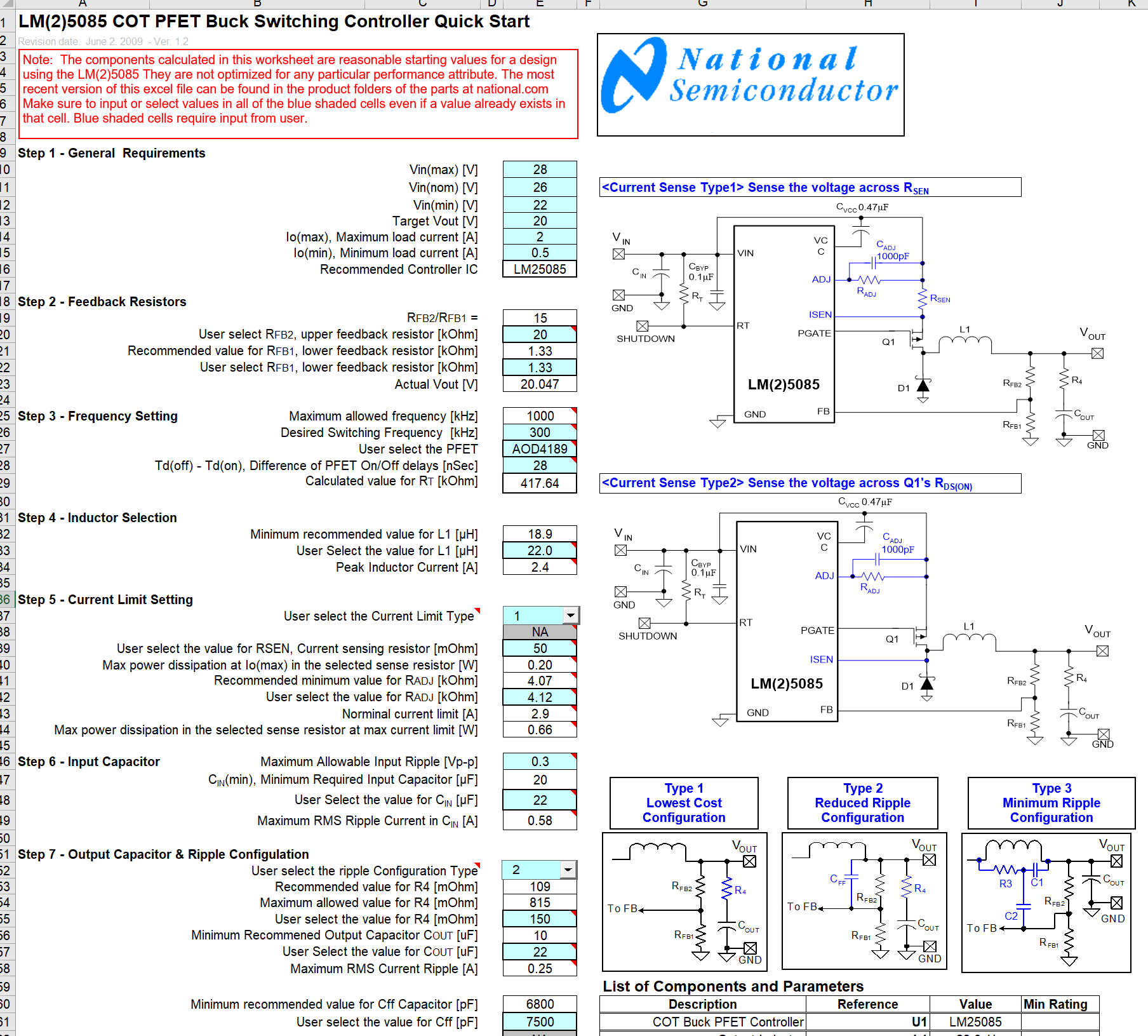

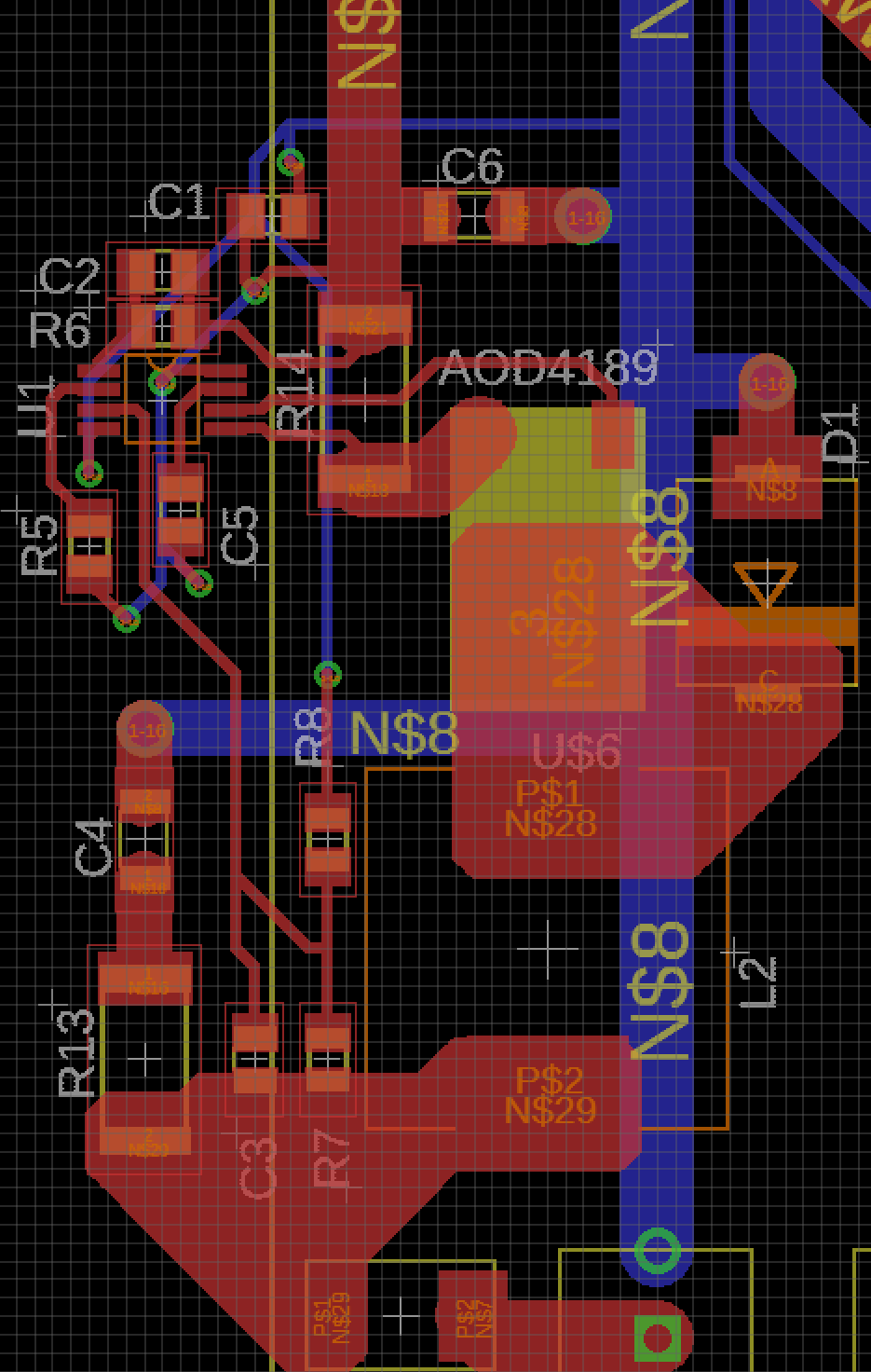

这里是我的原理图和快速入门电子表格。 我的手算与快速入门非常一致。 我将使用专用的感应电阻器和减少的纹波配置。

我将在26V 输入下进行测试、并且没有负载或7.5欧姆固定电阻器。 示波器位于 PGATE 上。

无负载:导通时间非常接近标称值2547ns、关断时间很长。 输出电压20.1伏、电流0安。

7.5 Ω 负载:导通时间相同、关断时间~30us。 输出电压约为3.75伏、电流为0.5安。

关断时间过长、导致电流低于所需电流。 根据数据表、关断时间应约为8us。

我尝试更改 RSEN 和 RADJ 的值、即使 RSEN 为0欧姆、也无法获得超过0.5安培的电流。 关闭时间不会低于30us。 我可以将电流减小到低于0.5安、例如、RSEN = 75 m Ω、RADJ = 2.2k、提供的电流为0.25安。

有什么建议吗?