工具/软件:WEBENCH设计工具

大家好!

我正在调试我的设计一段时间、但仍然不知道它为什么变得如此热。

我使用 webench 工具设计了2个电路、均采用 LM5085。 第一个、Vin=43-58V Vin 和24V/2A 输出变得太热、不再工作。 因此、该线程将更像是第二个线程、也是43-58V 输入电压和4.3V 1.8A 输出电压。

总之、我非常关注 Webench 建议的器件、该器件采用了 MOSFET、这是一种汽车版本的受支持 MOSFET。 此外、1uF Cin 是不同的器件型号、当然也具有类似的规格。

现在、在负载约为130mA 时、一些部件在打开后立即变得非常热。 本例中的"一些部件"是:二极管和 MOSFET 太热、无法触摸。 LM5085在20秒左右后也会变热、但我不确定它是否是由于它和二极管的良好热耦合而产生的、因为它本身是否变热。 让它运行几分钟时、电感器和其他器件也会变得很热、但我不确定它是否来自二极管和 MOSFET 的热量。

原理图如下:(我将器件型号放在器件旁边、德语文本不重要)

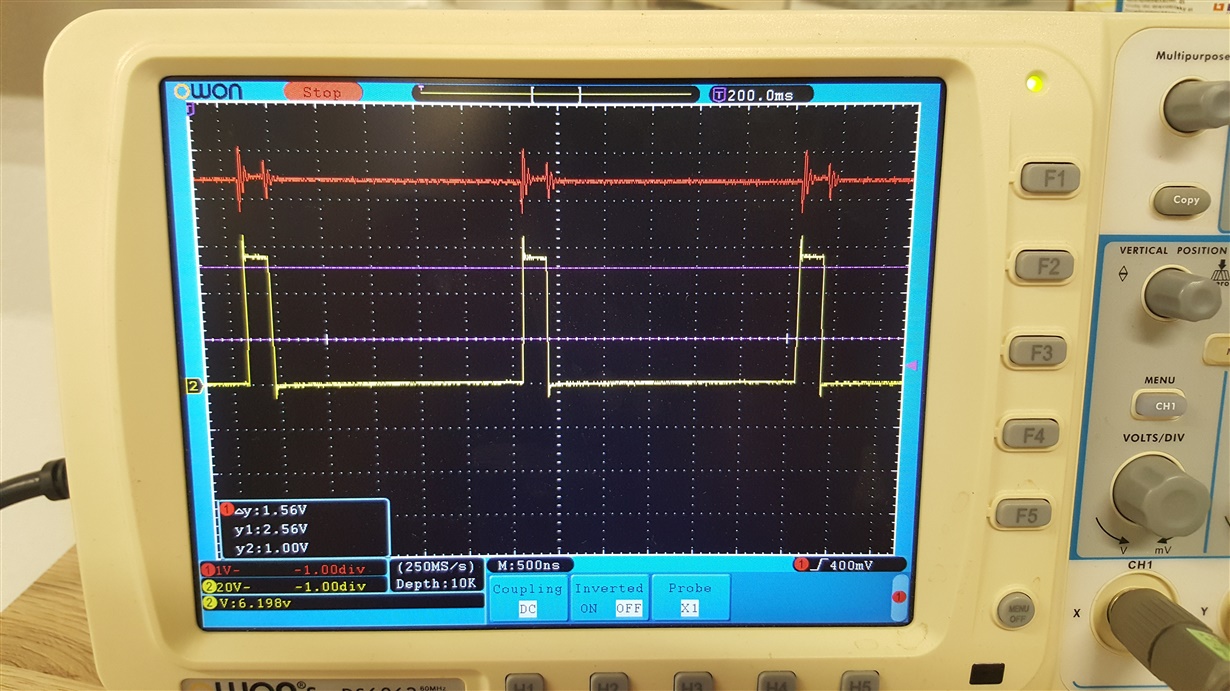

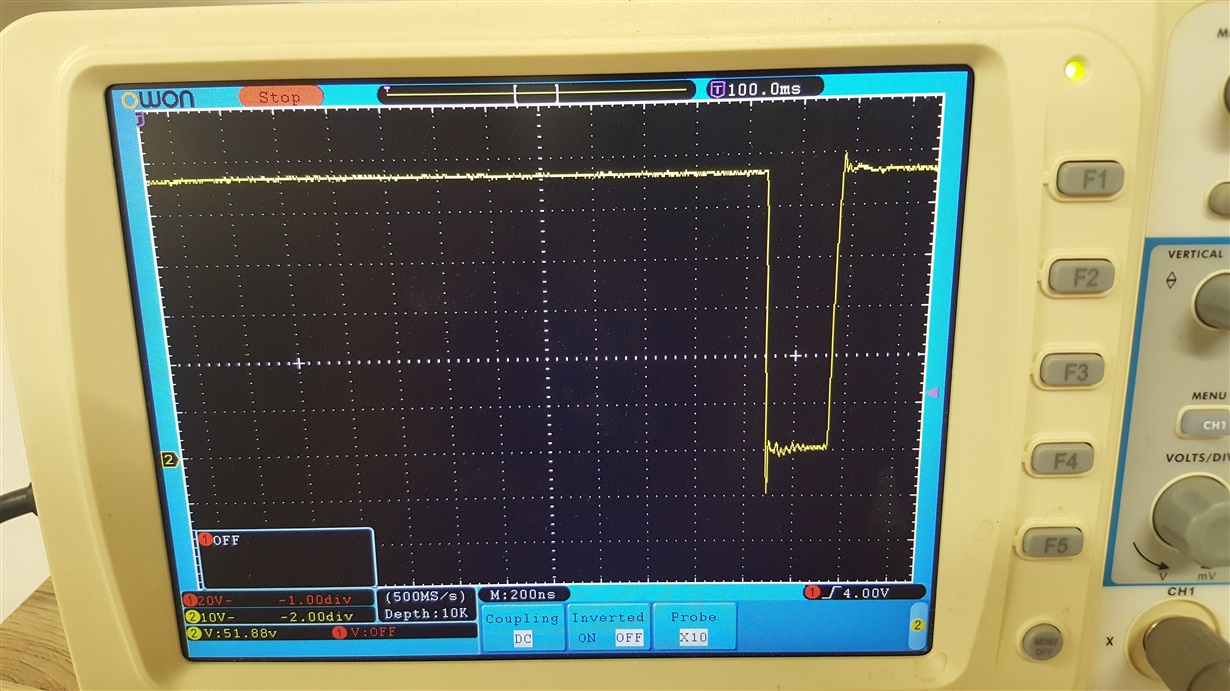

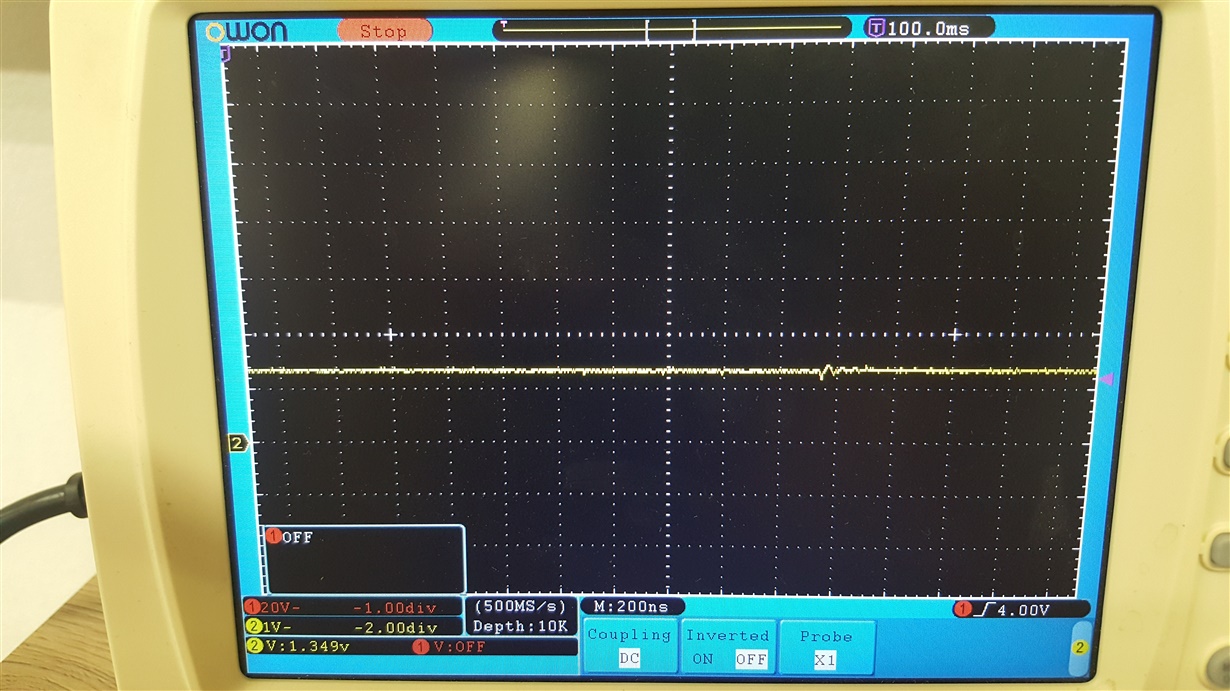

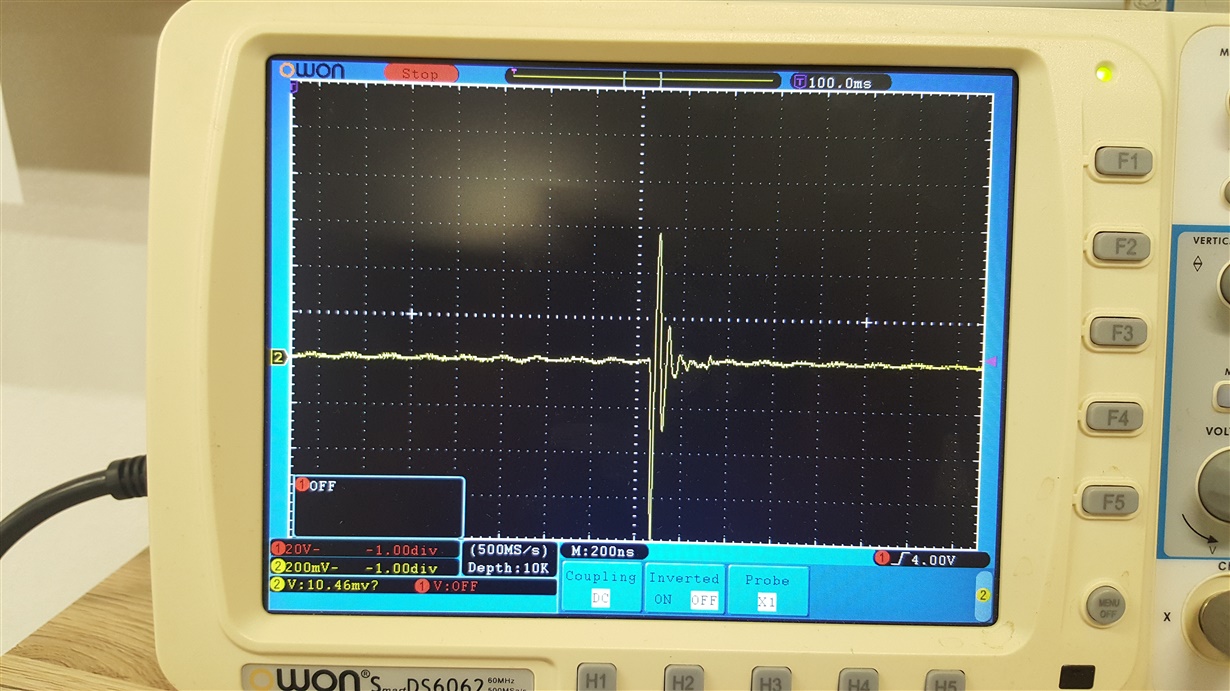

我认为您最重要的信息是波形:

上部 PIC:黄色 Vdiode 和红色 VCout

上部图片:VDS

上部 PIC:UFB

上部 PIC:分流器(分流器两端的电压、而非 GND)

我的问题是、为什么部件变得如此热以及我可以做些什么。 我感觉自己缺少一些明显的东西。 我非常确信更高的负载会烧毁电路。

感谢你的帮助!

Dominik