请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS65094 您好!

有关 TPS650942的 VDDQ 的问题。

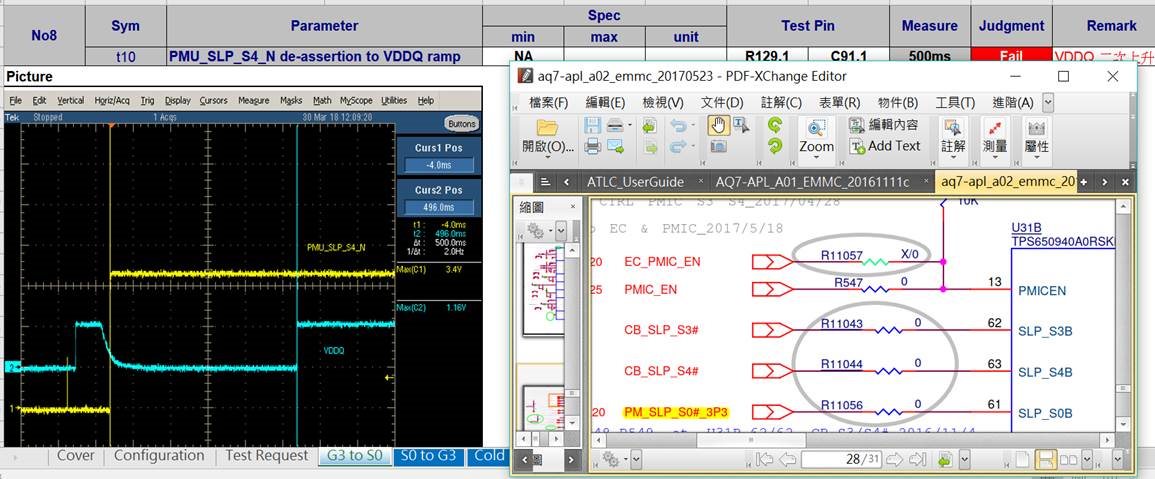

从 G3到 S0,我们发现 VDDQ 电压异常,如图2所示。

图片1和图片之间的区别是 S3和 S4信号。

图1、 S3和 S4从 SOC 到 PMIC

图2、S3和 S4从 SOC 到 EC 再到 PMIC (异常)。

我想知道哪个信号可能导致 VDDQ 异常。 (SLP_S4B 或……μ..)

S3、S4从 SOC 到 PMIC 控制。 这是正常的

S3、S4从 SOC 到 EC 再到 PMIC 控制。 (VDDQ 电压异常)

如果需要更多信息、请告诉我。 非常感谢您的帮助。