您好!

我还有一些有关 TPS3700-Q1的其他问题:

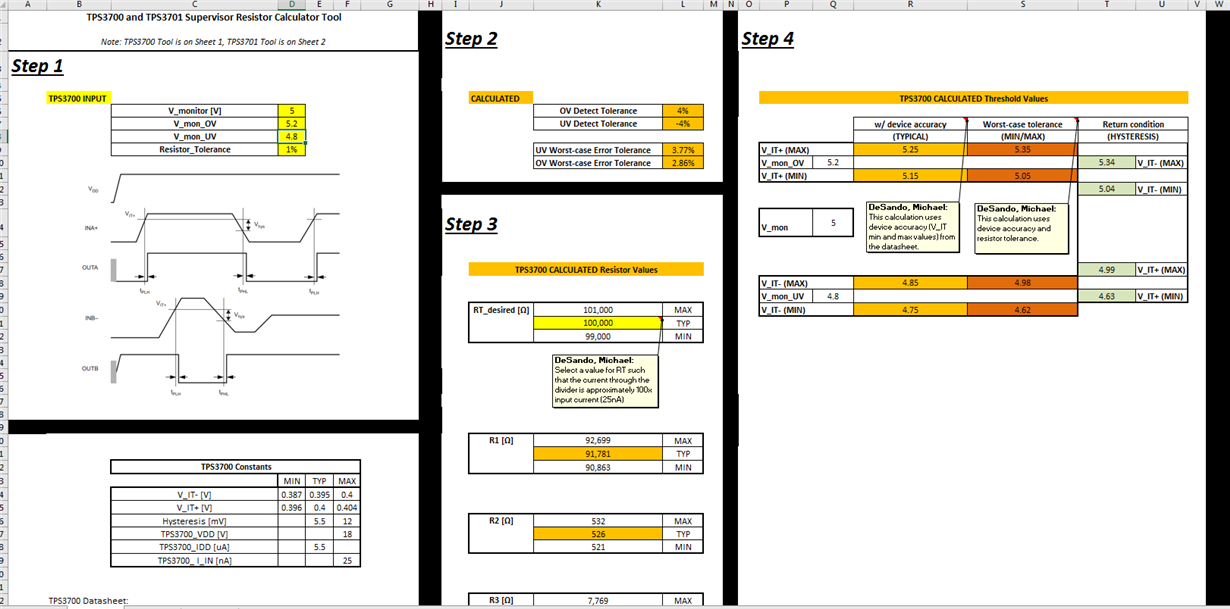

如何为 RT 选择合适的值?

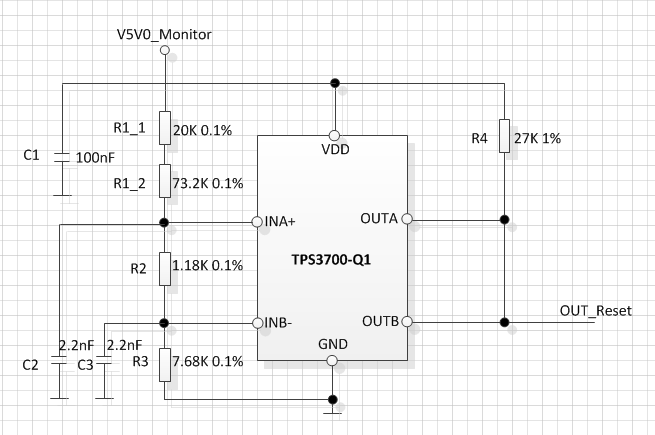

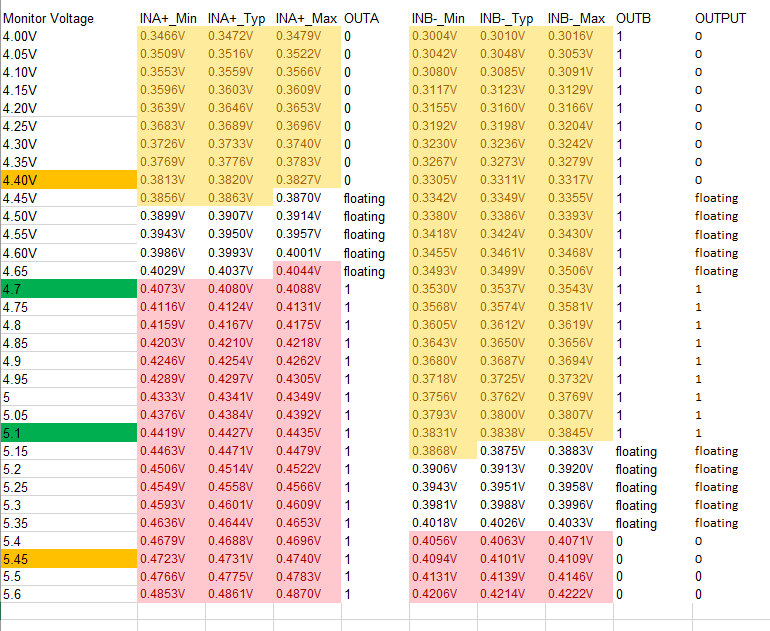

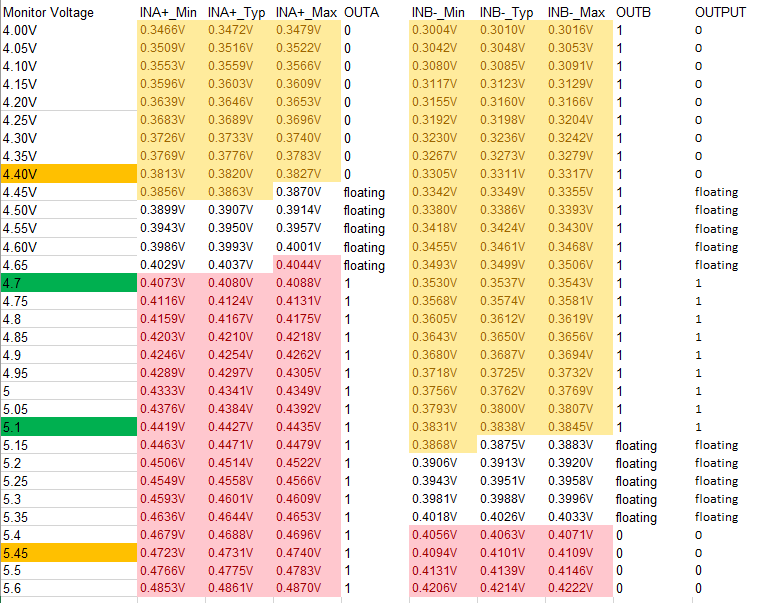

根据我的计算、如下所示:

假设:V (监视器)=5V

I (INA++ INB-)=25+15=40N A

RT≈V (监视器)/100* I (INA++ INB-)=5/100*40=1.25Mohm

我不确定我的计算是否适合 RT?

假设我们的产品不建议使用高于100k Ω 的电阻器、那么我的问题是我们是否可以选择比 INA+和 INB-端子上输入电流更高的电流?……

例如,1500次,因此 RT≈V (Monitor)/1500* I (INA++ INB-)=5/1500*40=83k Ω……是否正常? 还是会给器件带来不良影响?

2. R2的计算有两个公式,因此我们将计算出两个值…如何选择该值?

如何计算输出线上的上拉电阻器?

我的理解:RPU=(VPU-VLV)/IS (VPU:上拉电压;VLV:输出电压低 ;IS:输出灌电流)

对吗?

4.如果有必要在输入线路(INA+、INB-)上保留旁路电容器?

谢谢!!!