您好!

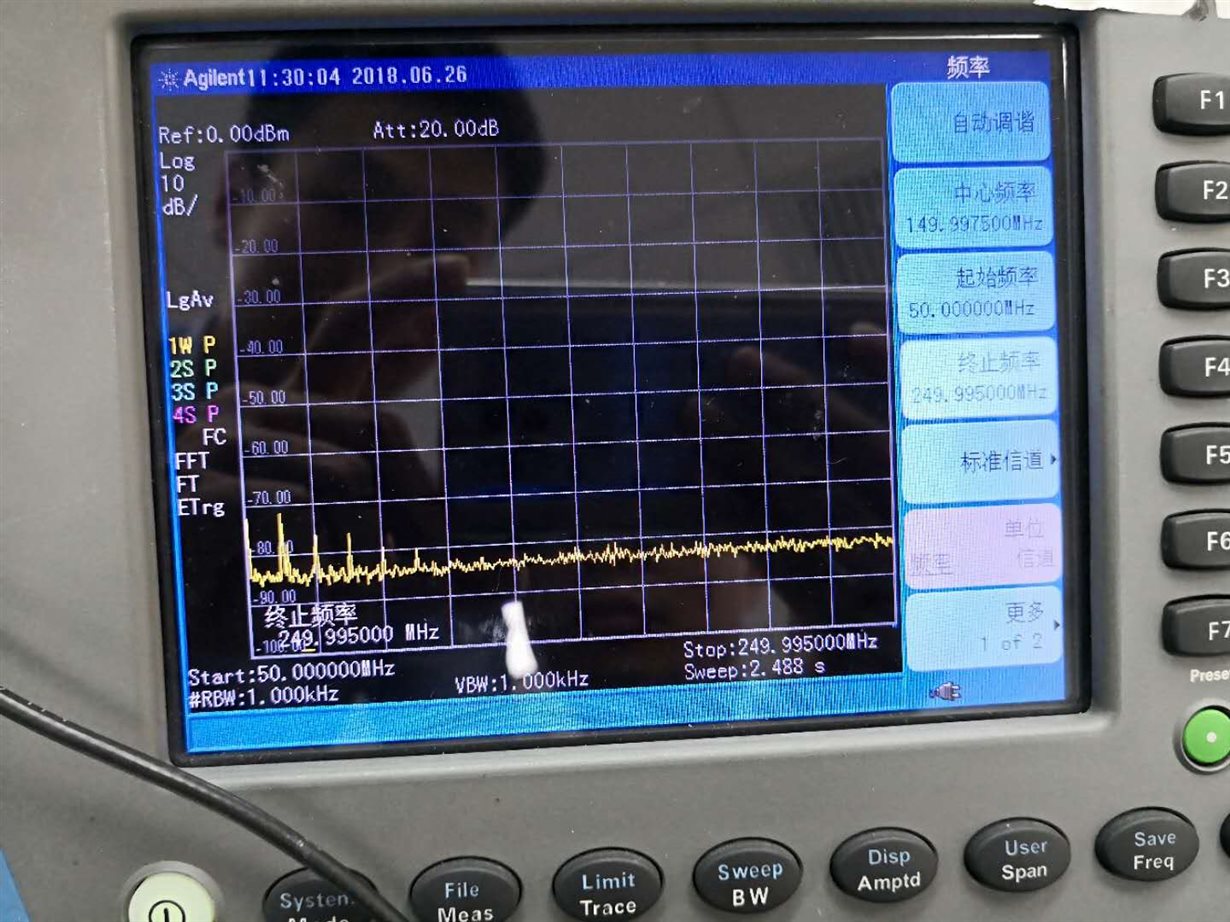

我的客户在其中一个显示模块中使用 LP8860-Q1、但他们未通过80M/90m/100MHz 下的 EMI 传导测试。

我想 LP8860是否有关系、因为它具有与故障频率非常匹配的10MHz 内部时钟。 我们使用近场频谱来测试 LP8860、我们确实找到了10MHz 峰值频率及其谐波。

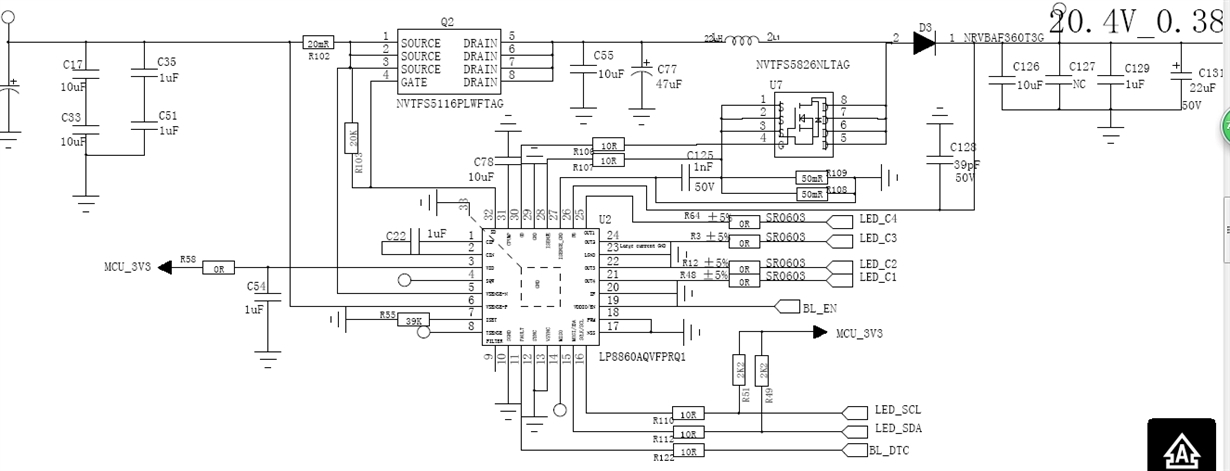

- 我根据客户的设置 EN_PLL=1连接原理图和 EEPROM、并且滤波器引脚悬空、这是根本原因吗? 我们能否 直接使用内部5MHz 示波器并禁用 PLL?

- 您能否仔细检查原理图和 EEPROM、10MHz 峰值频率的可能原因是什么?

- 对于升压输入和输出电容器、是否可以使用低于该值的电容器? 有哪些风险?

EEPROM 读数:

(T8U) 0x60、(T8U) 0xEA、

(T8U) 0x61、(T8U) 0x21、

(T8U) 0x62、(T8U) 0xDC、

(T8U) 0x63、(T8U) 0xF0、

(T8U) 0x64、(T8U) 0xC7、

(T8U) 0x65、(T8U) 0xf5、

(T8U) 0x66、(T8U) 0xF2、

(T8U) 0x67、(T8U) 0x77、

(T8U) 0x68、(T8U) 0x77、

(T8U) 0x69、(T8U) 0x71、

(T8U) 0x6a、(T8U) 0x37、

(T8U) 0x6b、(T8U) 0xB7、

(T8U) 0x6C、(T8U) 0x17、

(T8U) 0x6D、(T8U) 0xFF、

(T8U) 0x6E、(T8U) 0xB9、

(T8U) 0x6f、(T8U) 0x87、

(T8U) 0x70、(T8U) 0xC9、

(T8U) 0x71、(T8U) 0x72、

(T8U) 0x72、(T8U) 0xE5、

(T8U) 0x73、(T8U) 0xDF、

(T8U) 0x74、(T8U) 0x35、

(T8U) 0x75、(T8U) 0x06、

(T8U) 0x76、(T8U) 0xDE、

(T8U) 0x77、(T8U) 0xFF、

(T8U) 0x78、(T8U) 0x3E

此致。

东宝