主题中讨论的其他器件:TIDA-00778

非常奇怪的问题 成熟的软件 其他供应商的栅极驱动器在 Cboot 充电周期期间不会导致大电压浪涌。 此问题是指三相换向和24VDC 总线 电源在逆变器加载或未加载的情况下上升至超过90vdc。 自定义 PFC 解决 了80V-90V PWM 浪涌、控制直流总线电压。 这 是 Cboot 周期唯一能够成功的方法、更不用说 FOC 换向驱动连接的电机达到7600RPM 了。

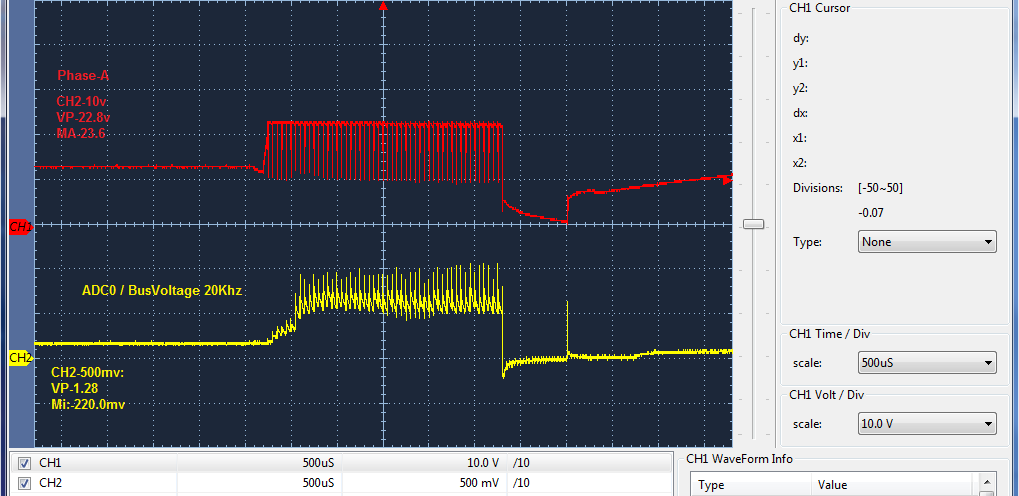

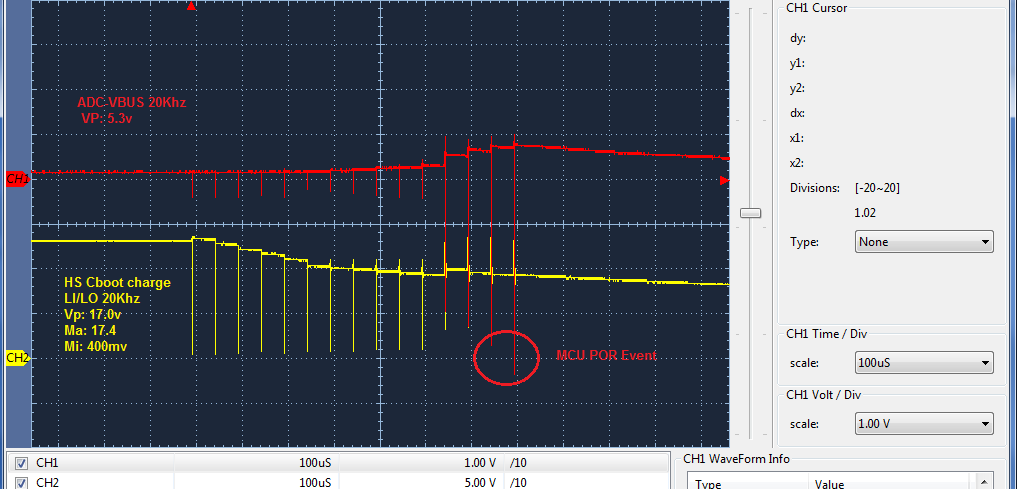

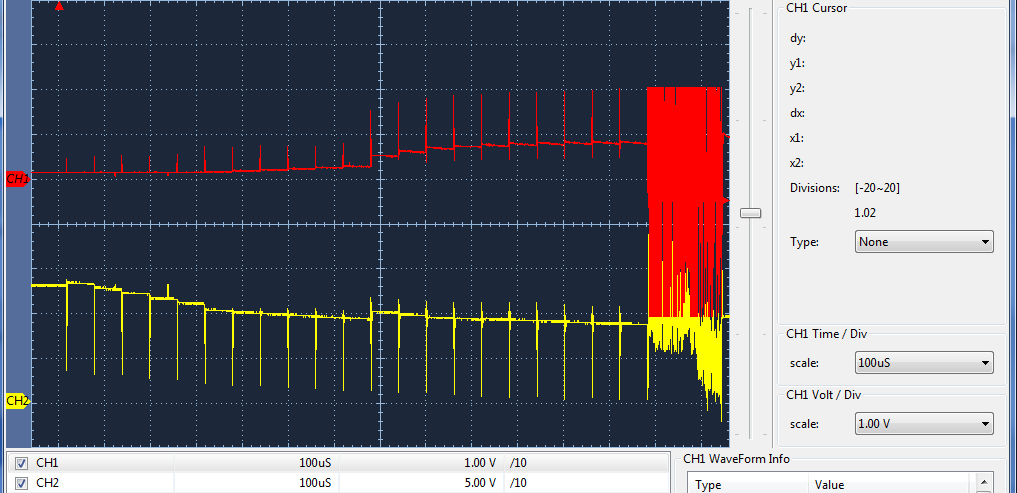

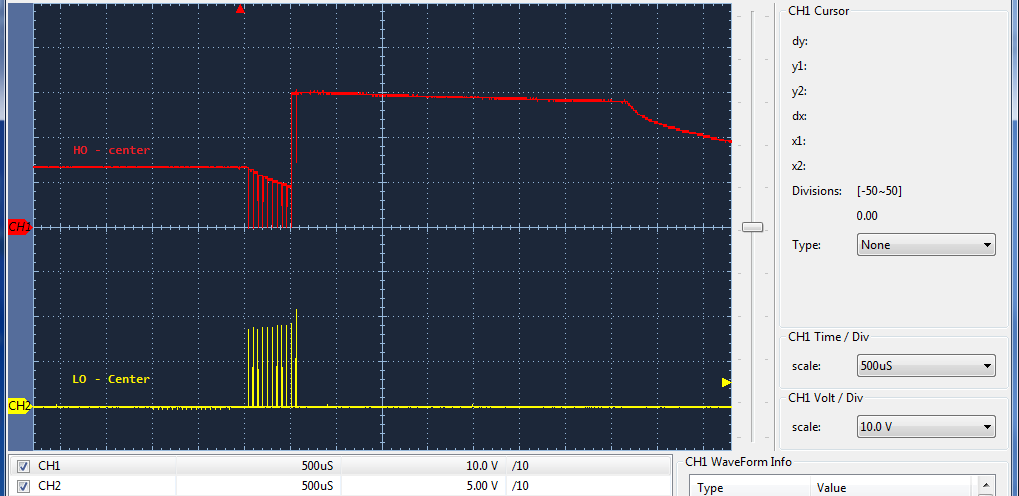

PWM 频率20Khz 驱动500ns Cboot 占空比(1%)、 用户可设置的充电时间1-255ms。 捕获低于 所采用 的单相(1/2电桥)、所有相位都类似于类似的模式 、但在 启用 PWM 故障处理后、信号会在2ms 内切断。 否则 、500ns Cboot 脉冲会非常突然地对 MCU 进行上电。 UCC 引脚4 (EN)在 该测试过程中始终保持高电平3v2 (已启用)。

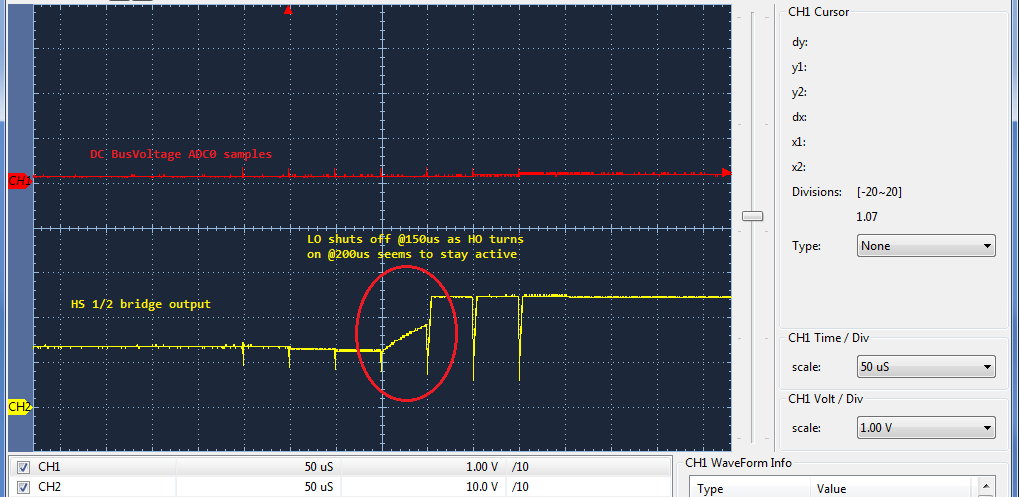

当 MCU PWM 控制块在 Cboot 周期内保持全部3个高电平(低电平)时、HO 驱动器如何在 Cboot 周期内保持打开? 我们是否不希望 H0侧在 Cboot 周期期间始终为低电平、或者我是否错过了1/2电桥击穿 的发生方式? 也许这3个栅极驱动器在某种程度上混乱、并且不遵循适当的1/2桥开关惯例。 LO 侧 栅极从接地端驱动脉冲上升沿 、从而产生下面的奇数波形式。 LO 侧在 我看来是正确的、但 HO 在 Cboot 周期期间保持有效、因此 HO 单个值是一些反转的方式。

CH2:ADC0通道输入 报告直流电压。 信号 表示 在 MCU 的不良 POR 之前、从24VDC 电源低侧/左侧产生的70-80V 峰值、最右。