Other Parts Discussed in Thread: CSD19506KCS, UCC27324

主题中讨论的其他器件:CSD19506KCS、

您好!

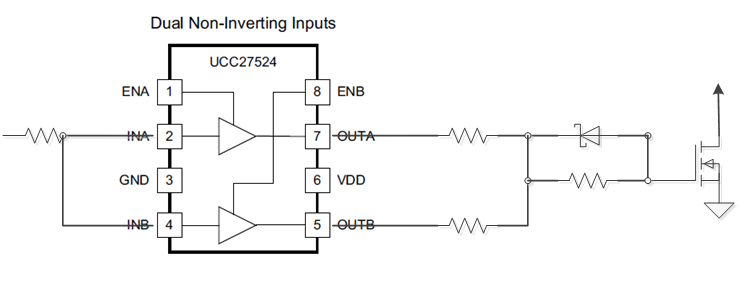

我有一个应用是单 个 UCC27324 (并行输出通道)并行驱动三个 CSD19506KCS。 每个 MOSFET 都有单独的6 Ω 栅极电阻器。 我想在关断期间降低 MOSFET 内部的开关损耗。 开关电流约为85A、开关电压约为60V。 UCC27324由15V 电源供电。 附加了测得的漏源和栅源波形。

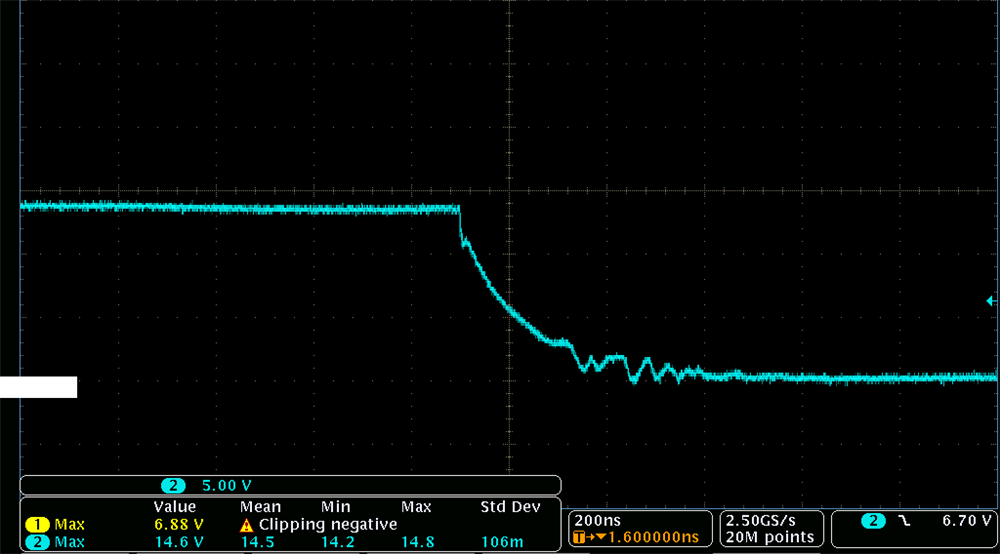

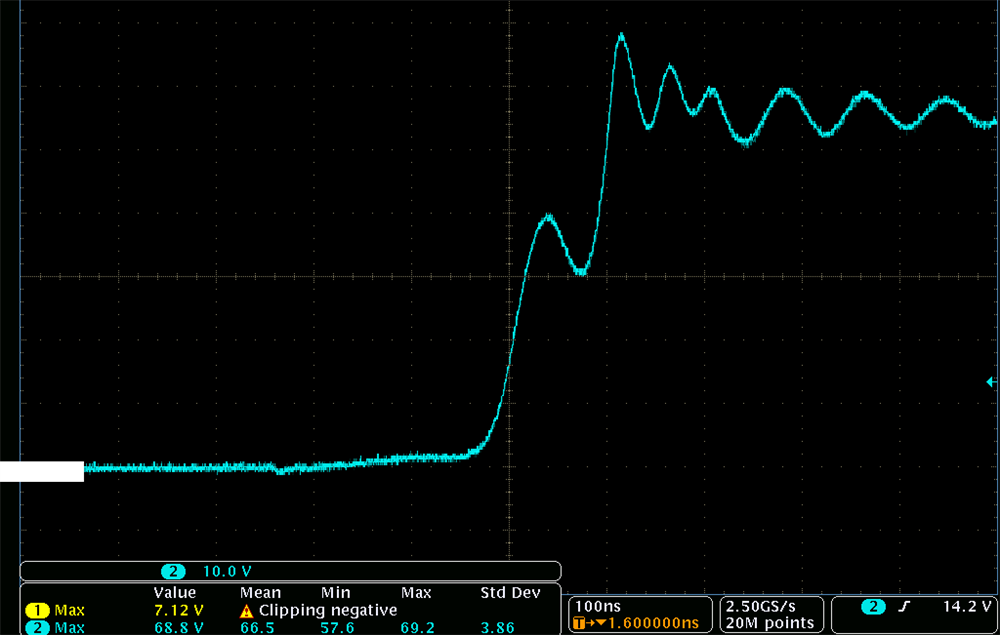

栅极-源极

漏源极

我想降低栅极电阻以提高非常慢的开关速度。 是否有针对这个组合的推荐栅极电阻器值?

UCC27324的数据表中规定了4.5A 的绝对最大电流和0.9 Ω 的最小输入电阻(在整个范围内)。 如果我将栅极电阻器减小到1欧姆、我计算出的总电阻为0.78欧姆(2个并联通道= 0.45欧姆+ 3个并联电阻器= 0.33欧 姆)。 忽略走线电阻和电感、我计算出的最大电流峰值为19A (15V/0.78A)。 这远高于数据表中的最大额定值(对于组合通道为8A)。 但是 、UCC27324数据表中的"灌电流测试电路"在容量和栅极驱动器之间的路径中没有任何限流电阻。

您认为是否可以将栅极电阻降至每个 MOSFET 1欧姆或甚至降至0欧姆?