主题中讨论的其他器件: UCC27531

您好 TI

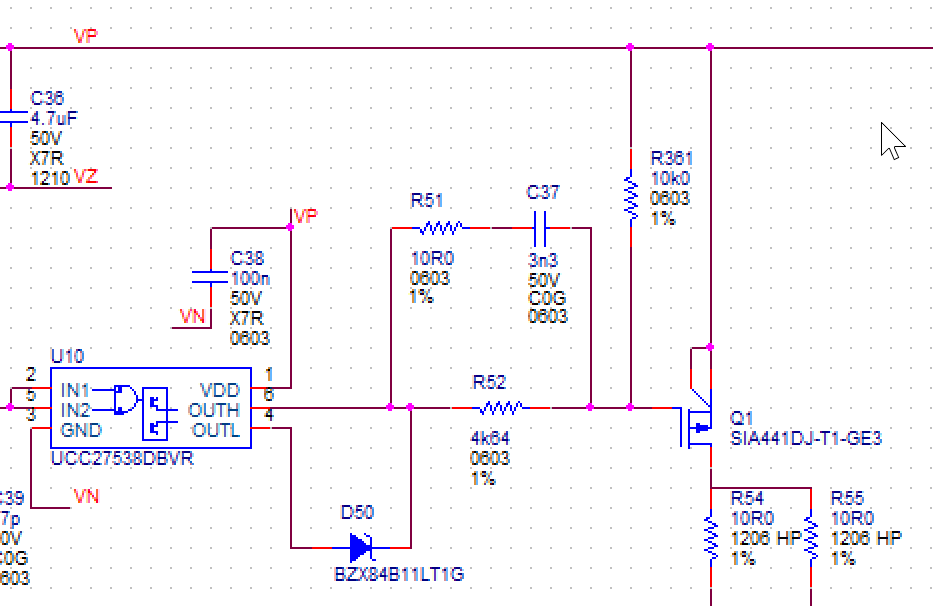

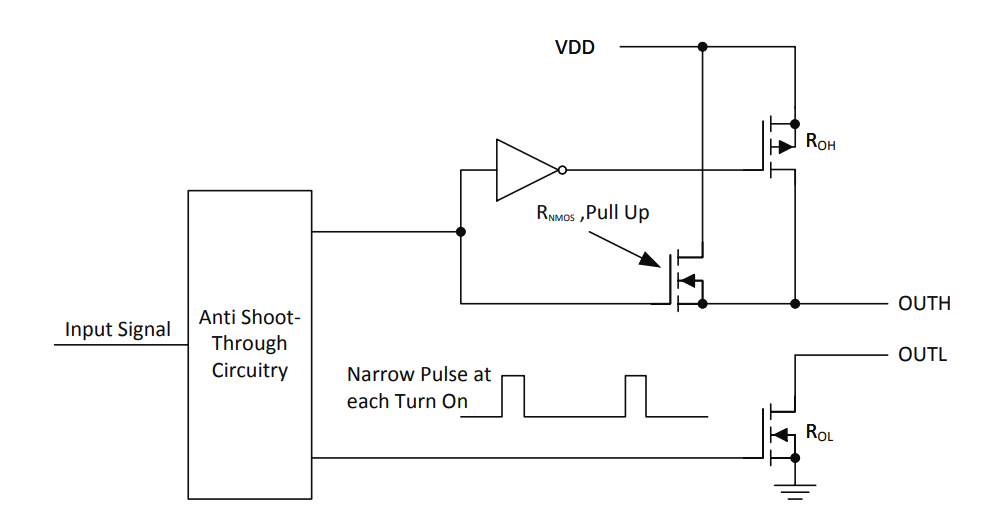

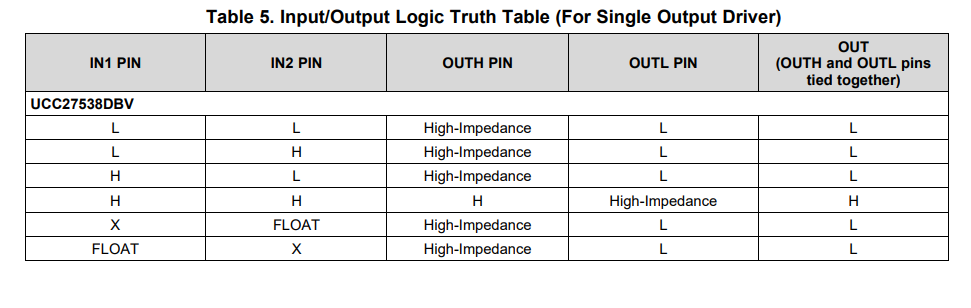

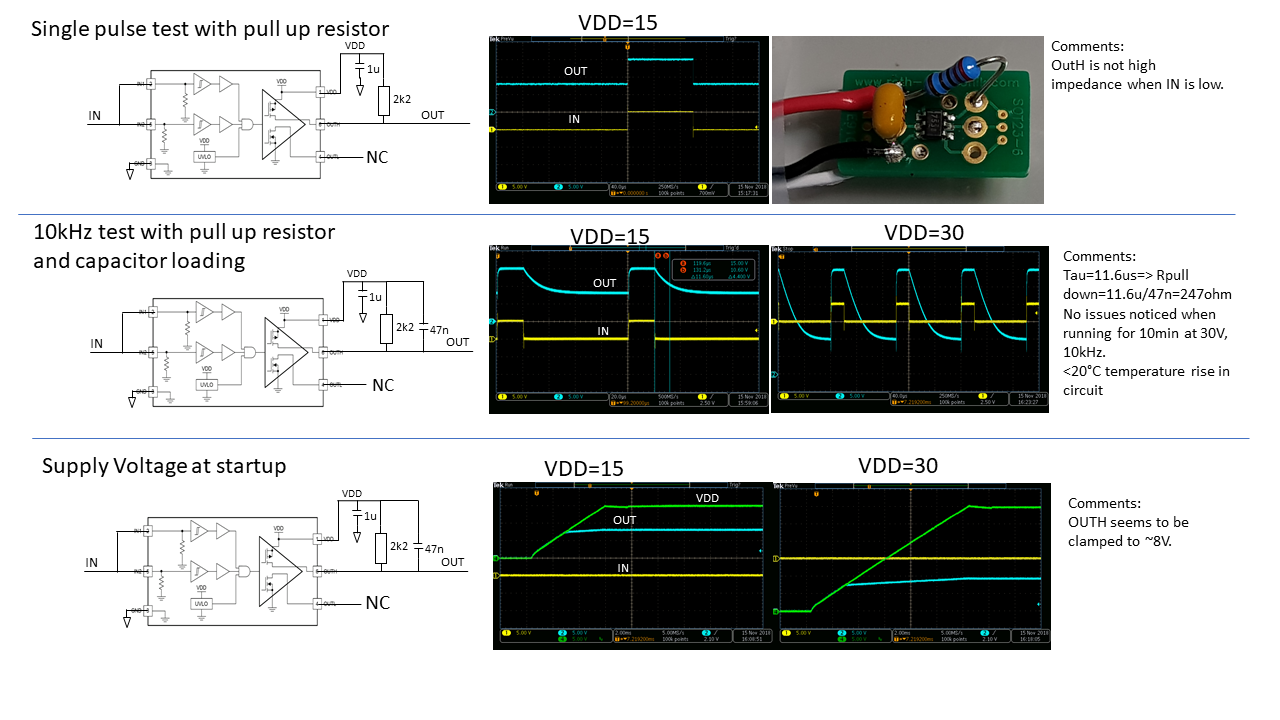

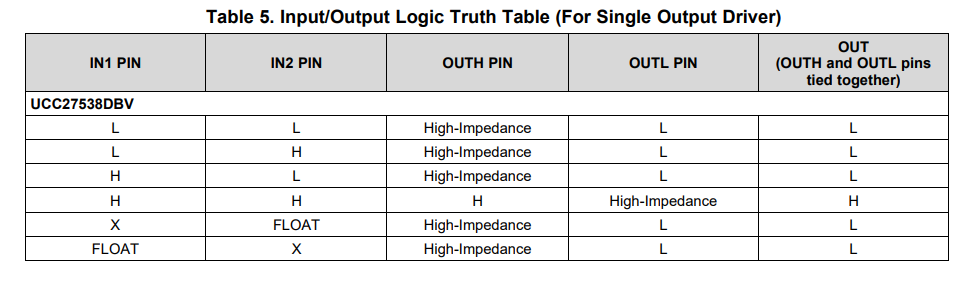

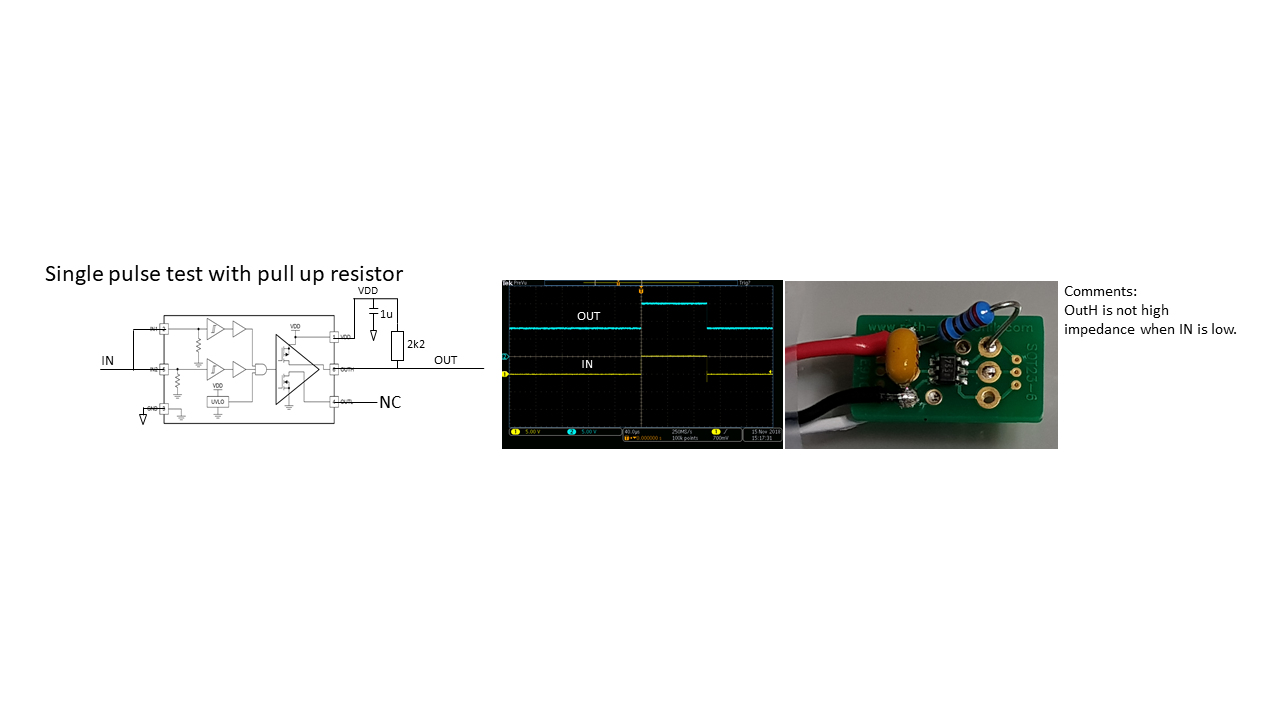

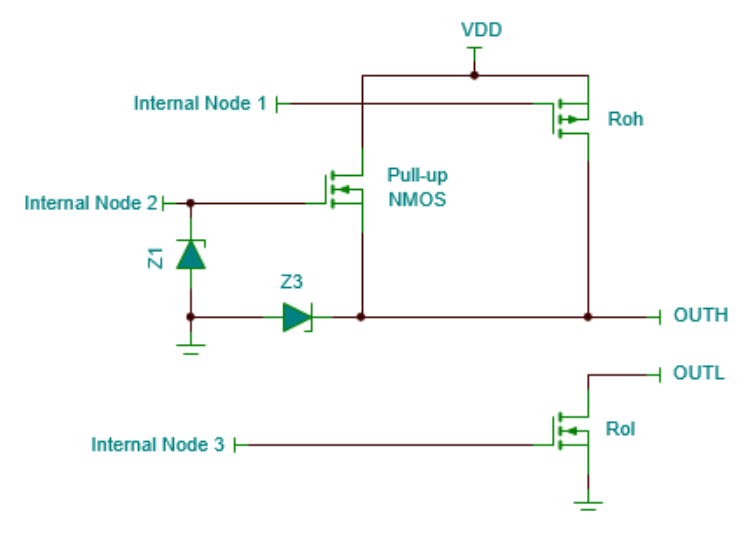

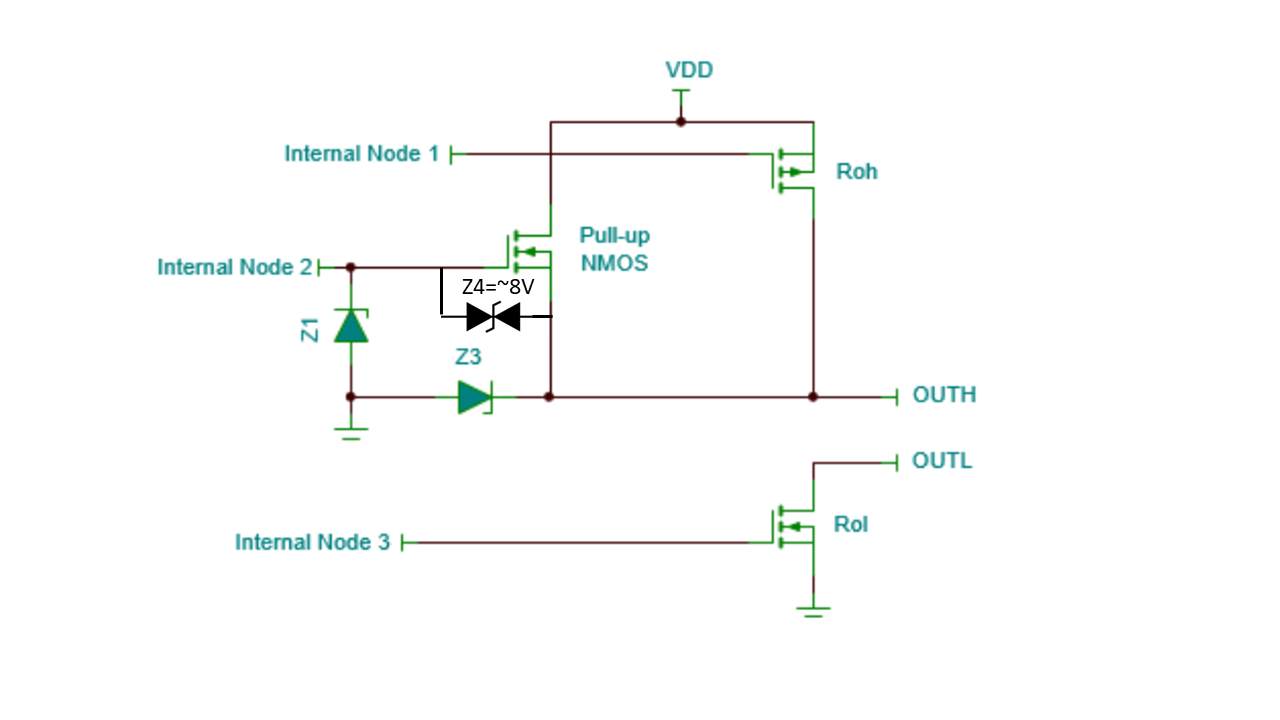

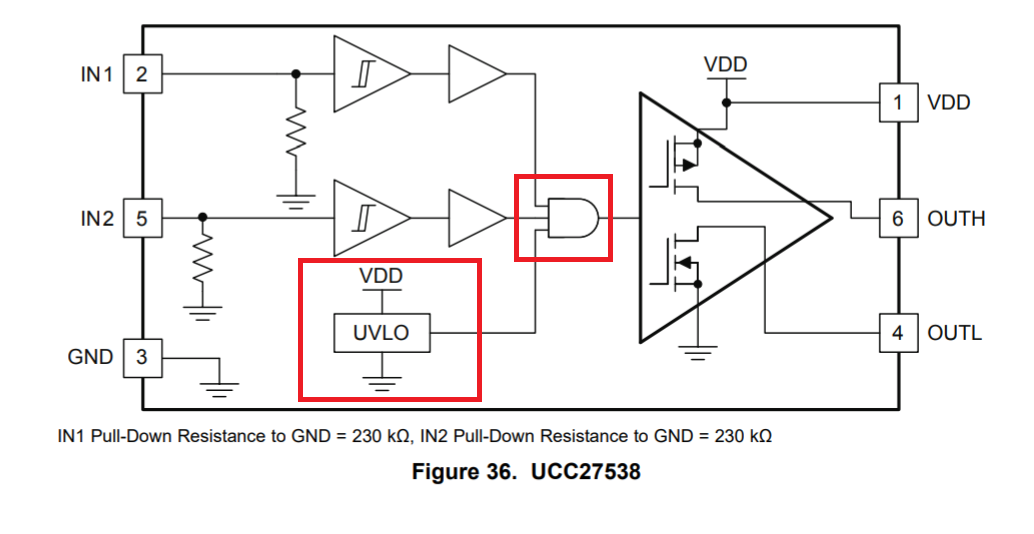

在 UCC27538中、是否有一些内部齐纳二极管从 OUTH 连接到 OUTL? (与下面的原理图中的 D50类似)

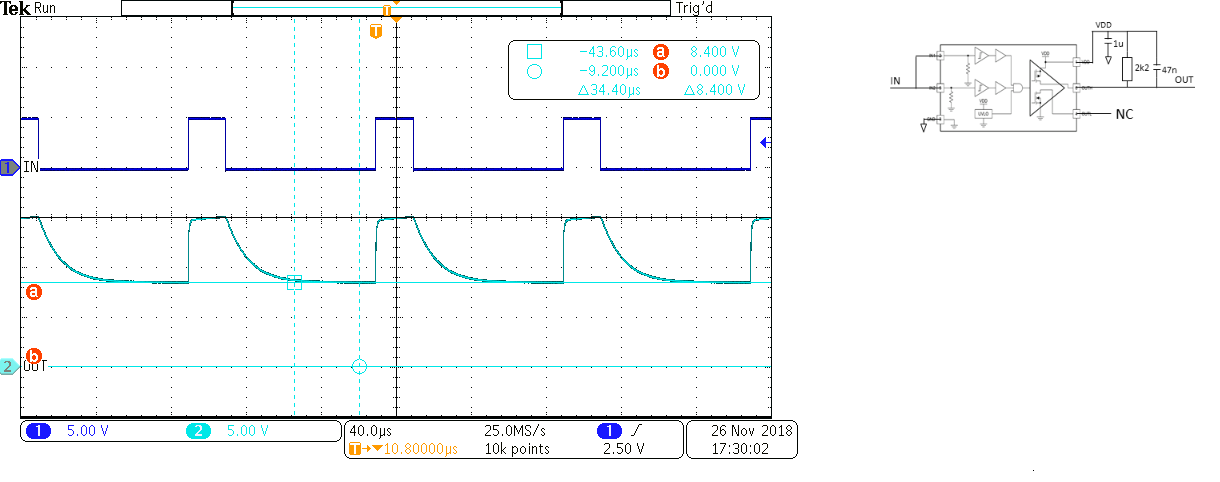

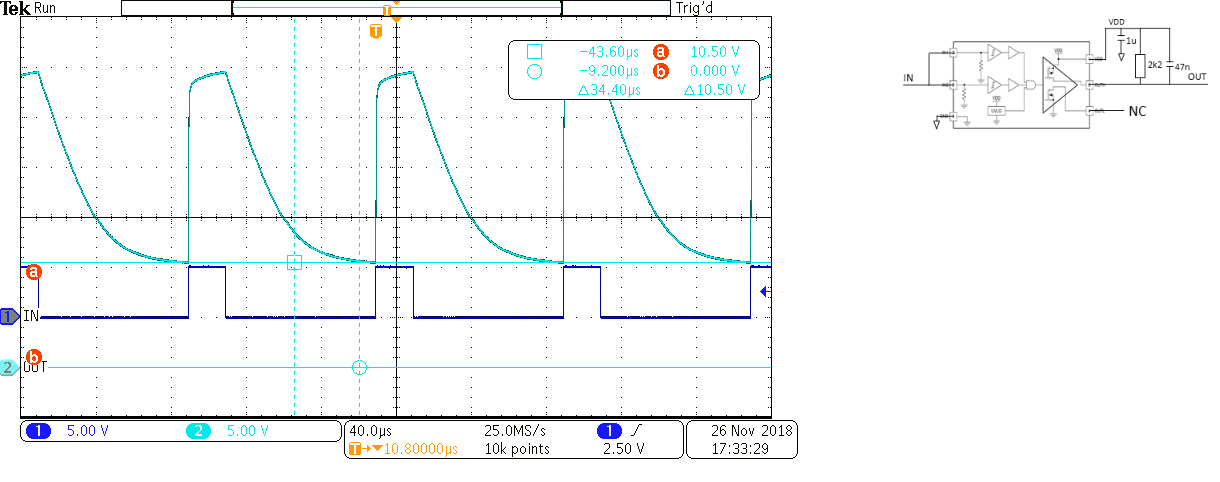

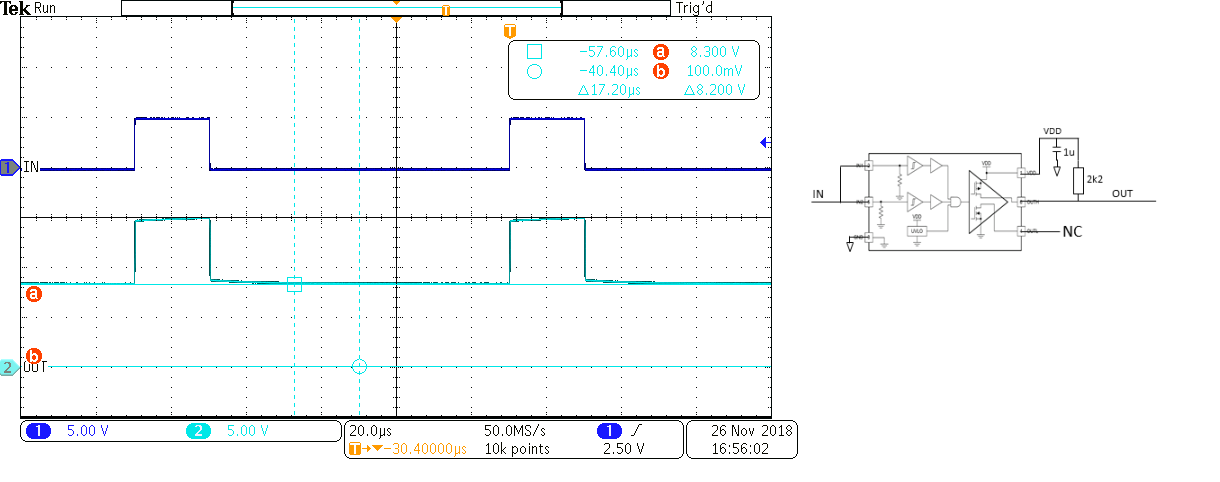

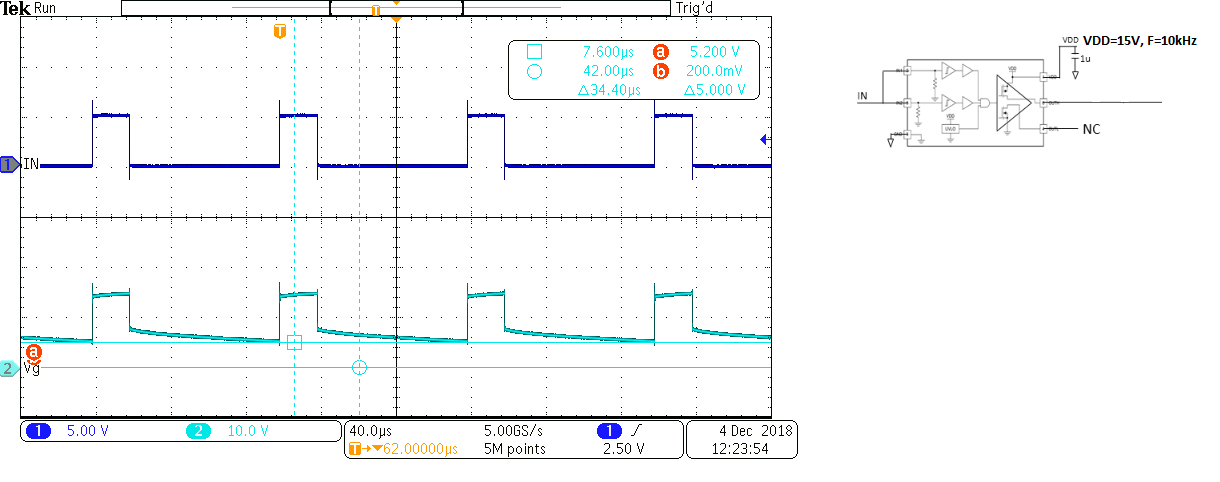

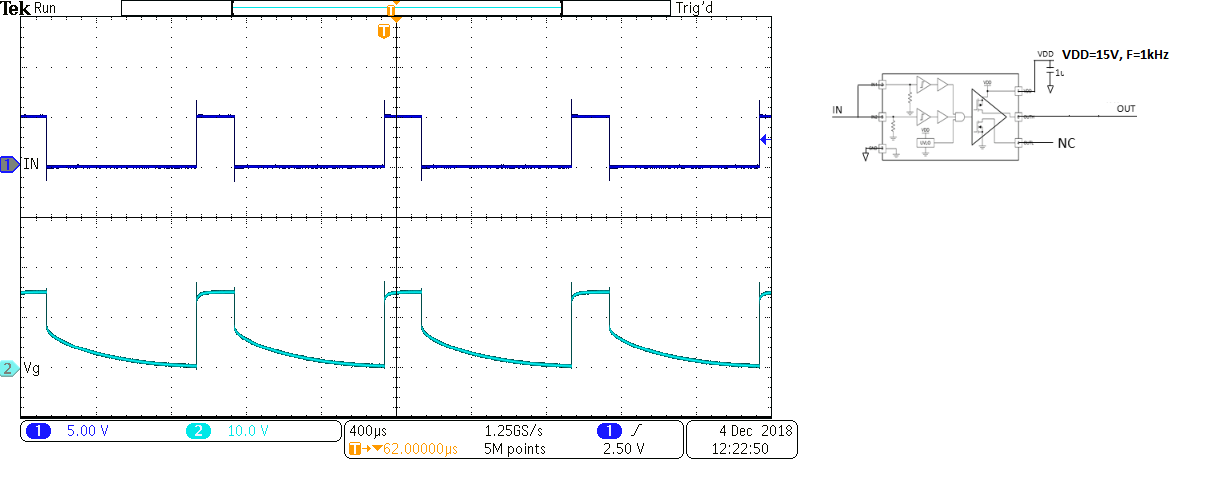

当输入变为低电平时、即使 OUTL 保持未连接状态、它似乎也会将 OUTH 下拉至~8V。 (在下面的原理图中、即使 D50已断开连接、也会发生这种情况)

我可以使用该齐纳二极管损坏器件吗? (I 开关频率极低、< 200Hz、并且仅通过10欧姆电阻为几 nF 充电)

请参阅以下原理图:(VP=21V、VN=0V)

此致、

调谐