您好!

我向客户询问 IOUTH = 200mA 和500mA 时 VOUTH 电压的最坏值。

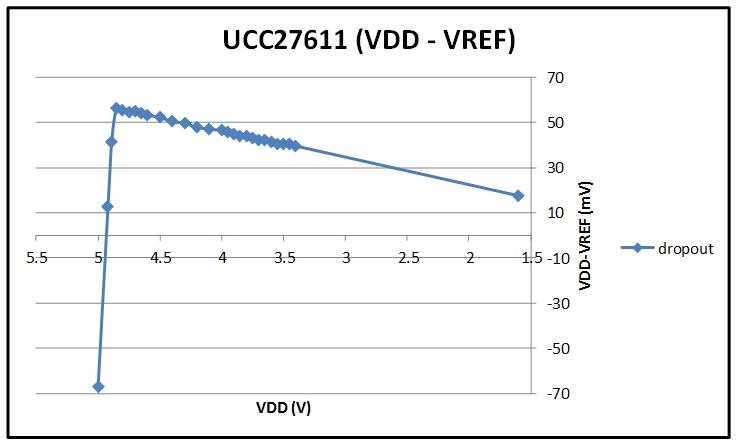

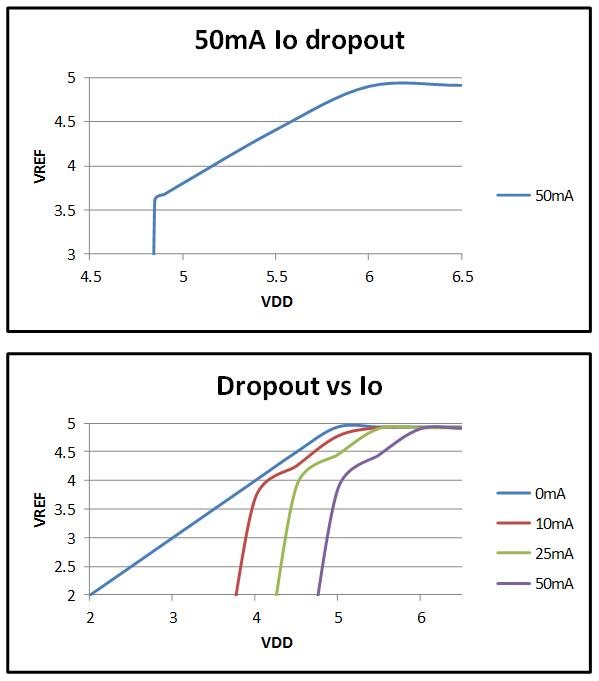

查看数据表特性、在 Ta=-40至140C 时、在 IOUT=-50mA 时、RU 被指定为最大2欧姆。

如果使用2欧姆作为最大 Rh、即使是200mA 和500mA、VOUTH 引脚上 VREF 的压降将为-0.4V (= 200mA)和-1V (500mA)。

在 IOUTH = 200mA 和500mA 时、我们可以这样估计最差压降吗?

或

是否有更好的估算方法来实现它? 如果您有任何实际数据或其他内容、最好是这样。

此致、

H.Someno