请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

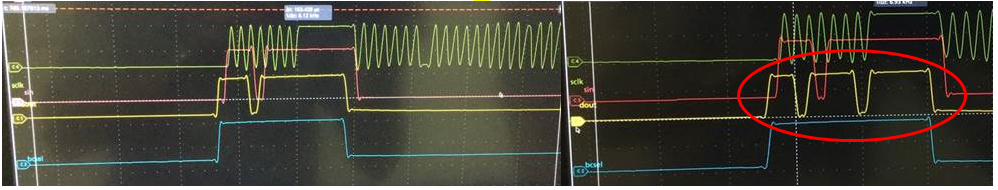

器件型号:TLC5943 TLC5943输出数据证实 TLC5943存在数据误解问题。 BC:EF 的写入值将被误解为 DE。

EF:1110 1111 DE:1101 1110 (只将一个位置移到左侧)

(确认正常的 SIN\SCLK 数据)

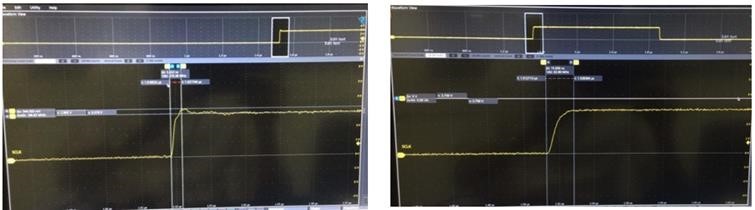

2、确认 SCLK 的当前设计存在0.35v 过冲、上升沿为3ns。 实验表明、SCLK 上几个 pF 电容器的并联连接(上升沿可延迟至大约10ns)、这可以改善数据误解。

需要 TI 帮助确认:

TLC5943对 SCLK 上升沿延迟有特定要求、3ns 的上升沿是否满足 IC 设计要求?

2.并联电容器是否可以延迟 SCLK 的上升沿从根本上解决数据误解的问题?

3.在测试过程中,发现当 SCLK 为高电平时,如果 BCSEL 在正常时间运行,时间序列中会有风险?

谢谢