尊敬的 TI、(可能是 Gordon):

在上一篇文章中使用的同一电路中、我有两个 TPS43351-Q1。 一个是主器件、其 SYNC 引脚连接到其 VREG 引脚、以便始终处于 CCM 模式。 主器件的通道2低侧栅极驱动输出、引脚 Gb2、被连接至第二个 TPS43351-Q1的 SYNC 引脚。 它们都在工作、但它们的开关频率不同步。 我在主器件的 Gb2和从器件的 SYNC 之间有足够的 R-C 低通滤波器空间、但 Gb2波形非常干净。 主机已启用扩频。 这是否可以防止从机的 PLL 锁定? 我在350kHz 频率下将一个电平为0至5V 的50%方波连接到了从器件的 SYNC 引脚、这种连接方式非常完美。 第二件事 II 想知道 SYNC 引脚是否需要50%方波-主器件的 Gb2输出不是50%占空比。

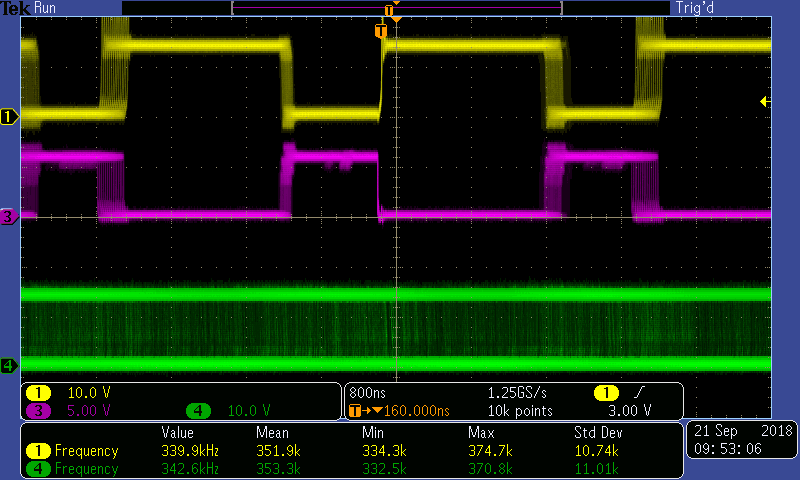

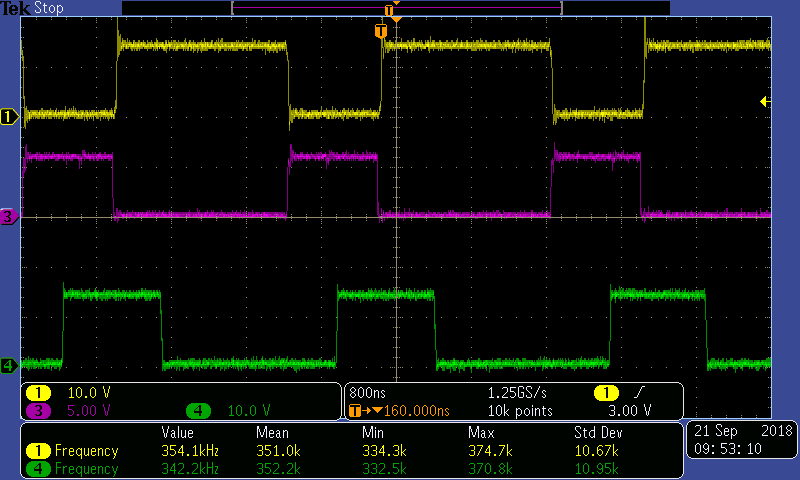

Ch.1 =主器件的 SW1、Ch.3 =主器件的 Gb2引脚和从器件的 SYNC 引脚、Ch4 =从器件的 SW1

该图显示、Gb2/SYNC 的上升沿与从器件的 SW1不对齐、而是在从器件与信号发生器同步时对齐。

谢谢、

Chris