请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLV702-Q1 您好!

我们使用 TLV70215并查看输出电容器 ESR 要求。

数据表指出、等效 ESR 应小于200m Ω。

我们在输出端具有10V 1uF 多层陶瓷电容器(MLCC)、并在 FPGA 周围有一些本地100nF 旁路电容器。

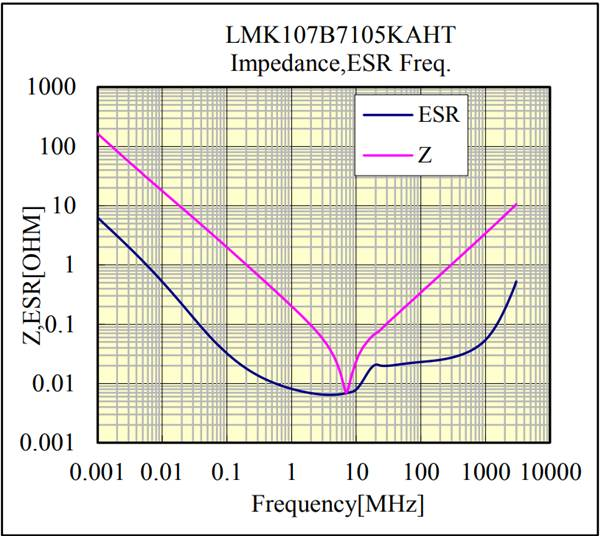

<<下方复制的频率图像上的 ESR >>

我们应该在数据表曲线中评估 ESR 的频率范围?

该曲线显示直流电阻大于6欧姆、7MHz 时大于0.7欧姆。

100nF 旁路电容器、它们具有相似的 ESR 曲线。 即使我们认为它们都是并联的、我们在直流时稳压器的输出电容器上也有大约2欧姆的有效 ESR。

如果这是问题、请告诉我们吗?

如果是、您能否推荐一个更好的输出电容器?

谢谢、Keith