请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS3700 大家好、

如果未使用 TPS3700的 INB (-)引脚、应如何设置 INB 和 OUTB 引脚?

此致、

石田山

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、Masound-San、

感谢您的回答。

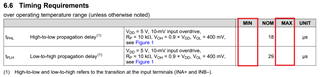

以下 tPHL 和 tPLH 仅为标称值。

请告诉我最小值和最大值。

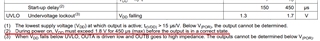

µs 还介绍了[(2)在上电期间、VDD 必须在450 μ s (最大值)内超过1.8V、然后输出才处于正确状态。] 数据表中。

我知道这是红线时间、但它是正确的吗?

450us 的启动延迟是否表示输出达到正确逻辑状态所需的时间?

在这个图表中、我了解 OUTA 的初始逻辑是低电平、因为 INA+是低电平。

启动延迟的最小值是多少?

此致、

石田山