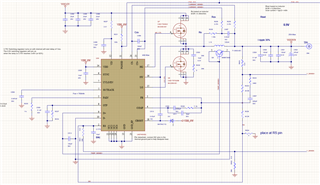

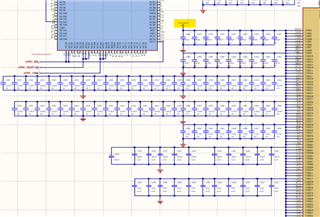

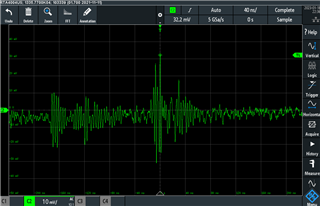

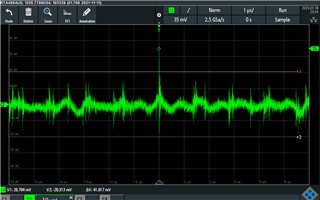

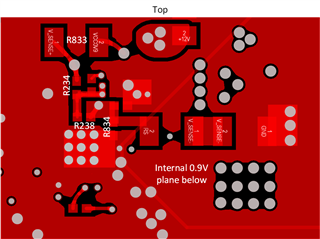

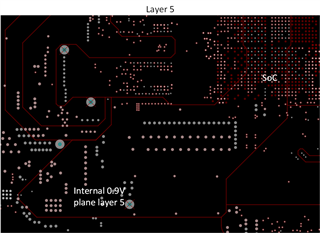

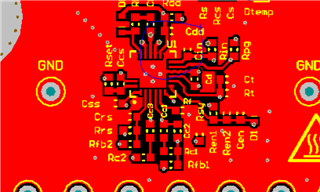

我看到 LM27403设计在较低温度下不稳定。 这似乎来自补偿环路滤波器组件选择。 在 机柜外的-40C 至55C 工作环境温度范围内、使用此稳压器的90%设备都可以正常工作。

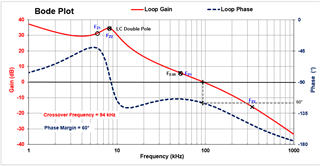

当我将交叉频率从46kHz 移动到100kHz 时、不稳定性会变差。

数据表中的值

- 该°的目标为50°至70 Ω、这被视为理想值。

- 环路交叉频率通常在开关频率的十分之一到五分之一之间进行选择。

当 fsw=700kHz 且值(100kHz)介于70kHz 和140kHz 之间时、应该会更好。 相补角为60度、介于50和70之间。

和当前设计的一样

根据数据表的建议、我将交叉频率更改为接近100kHz、介于 Fsw 的10%和20%之间

拨入此号码的最佳方式是什么?

TIA

John Fagerlund