请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS389006-Q1 主题中讨论的其他器件: TPS389006

你(们)好。

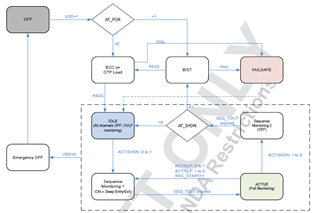

客户正在进行 tps389006-Q1序列测试。

我们发现 ACT 被单独下拉约1.5ms、波形如下所示。

测试条件。

1.如果 ACT 上升沿在 VDD 上升沿之前

2.当 VDD 达到约3.3V 时,ACT 信号被下拉。

由于 ACT 输入信号也用作其他器件的使能信号、它会导致 另一个器件出现异常的开/关。

请帮助我们仔细检查 tps389006-Q1是否正常运行?

BRS、

Shubiao