主题中讨论的其他器件:LM5155

您好、专家、

有关 LM5155 ULVO/SYNC 引脚功能的信息、请咨询您。

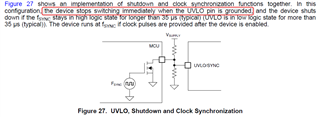

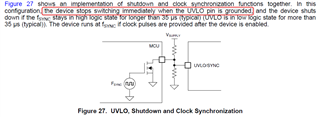

在数据表中、可以看到、外部同步时钟必须将 UVLO/SYNC 引脚电压下拉至1.45V 以下、但也可以看到、当 UVLO 引脚接地时、器件会立即停止开关。

那么、我想、如果外部同步时钟在 PWM 信号的低电平状态期间将 UVLO/SYNC 引脚电压驱动为0V、会发生什么情况? LM5155器件是否会停止开关?

谢谢!

Eden Wen

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、专家、

有关 LM5155 ULVO/SYNC 引脚功能的信息、请咨询您。

在数据表中、可以看到、外部同步时钟必须将 UVLO/SYNC 引脚电压下拉至1.45V 以下、但也可以看到、当 UVLO 引脚接地时、器件会立即停止开关。

那么、我想、如果外部同步时钟在 PWM 信号的低电平状态期间将 UVLO/SYNC 引脚电压驱动为0V、会发生什么情况? LM5155器件是否会停止开关?

谢谢!

Eden Wen

您好、TI 专家、

实际上、我将此问题发布到了 Ethon.

我已经查看了数据表、但我的脑海中仍然存在一些困惑、您能帮助查看我的问题下面的内容吗?

根据您在数据表中指出的、它表示、如果 Fsync 处于高逻辑状态、那么器件会立即停止开关、但是、当我们为 LM5155提供外部时钟时、Fsync 肯定会被拉高、那么器件将停止开关?

此外、在数据表中还显示、如果 Fsync 在超过2个开关周期内保持高逻辑状态、器件将进入待机模式。 不过、在这里我可以理解、我的问题是、在 LM5155中、它取决于开关周期或固定持续时间? 原因是外部频率可以在100kHz 至2.2MHz 之间变化。

此外,根据数据表,似乎只有当器件进入待机模式(不要考虑关断模式)时,才不会进行切换。 那么为什么当 Fsync 处于高电平时器件立即停止开关、并且只有当 Fsync 保持高电平并持续2个以上的开关周期才能进入待机模式?

对于关断模式、数据表非常清楚地说明、只有当 UVLO 电压低于 EN 阈值的持续时间为35uS 时、器件才会进入关断模式。

您好、Chang、

我再次浏览了数据表说明、并同意在某些地方可以更好地描述这一点。

当数据表显示它立即停止开关时、这意味着只要 UVLO/SYNC 引脚保持低电平、当前周期将结束、但不会启动新周期。

当 UVLO 处于高电平超过2个时钟周期时、UVLO/SYNC 停止开关适用于同步逻辑不将 UVLO/SYNC 引脚下拉至低于0.7V EN 电平的情况。 在这种情况下、高电平状态检测被激活。 但是、如果 UVLO/SYNC 引脚被拉至0V、器件将被禁用。

此致、

Stefan