主题中讨论的其他器件:TPS389006、 TDA4VH、 TPS6594-Q1

尊敬的 TI 专家:

在 TPS389006 Safetymanual 中、我们无法实现以下 SA、因为在当前系统设计中、如果 IRQ 拉低、系统将关闭。

是否有任何方法可以检查错误状态、但不影响 IRQ 状态(如果禁用了 int)?

BR

小威

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 TI 专家:

在 TPS389006 Safetymanual 中、我们无法实现以下 SA、因为在当前系统设计中、如果 IRQ 拉低、系统将关闭。

是否有任何方法可以检查错误状态、但不影响 IRQ 状态(如果禁用了 int)?

BR

小威

尊敬的 Andrew:

感谢你的帮助。

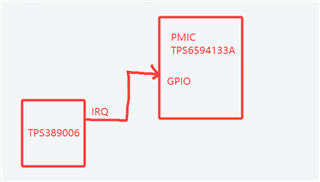

当前系统设计遵循,它来自 TDA4VH 的 PDN 设计。

"

在 MCU_PWR_GRP_IRQn (连接到 GPIO10)的下降沿、PMIC 将执行所有电源轨有序关断。

在 MAIN_PWRGRP_IRQn (连接到 GPIO8)的下降沿、PMIC 将关闭为 SOC 供电的电源轨、但使与为 MCU 供电相关的电源轨保持启用状态。 (我们的系统将关闭)

”

BR

小威

尊敬的 XW:

我不确定您如何 使用某种缓冲系统来检查 NIRQ 功能、而这种缓冲系统不会给您的电路添加单点故障。 如果有一种暂时禁用 GPIO8/GPIO10功能的方法、您能否检查另一个 E2E 线程。

或者、如果有 不同的 GPIO 可以连接 NIRQ、而这些 GPIO 可以向 GPIO8/GPIO10发送信号、但只有在您完成 NIRQ 功能测试后、您才能检查另一个线程?

谢谢、

Andrew