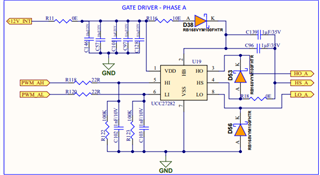

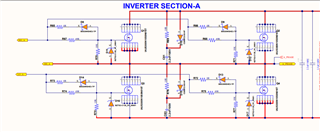

我使用 UCC27282栅极驱动器来打开半桥中的 MOSFET (将三个栅极驱动器用于三相逆变器)。 MOSFET 器件型号为 IAUS300N10S5N015T。 死区时间已配置为2us。 一旦高 侧 PWM 打开、在2us 低 PWM 关闭后、我会在 LO 引脚上看到一个小电压尖峰。 由于我没有将逆变器连接到电机、因此没有电流流入逆变器。 尖峰高达2V。 请任何人解释原因。 我将附上栅极驱动器和逆变器部分的原理图。

Rgon = 10欧姆

Rgoff = 2.7 Ω

VDC=48V

VDD (栅极驱动器电压)=12V

软件 频率= 10kHz

注意:并联使用2个 MOSFET