您好!

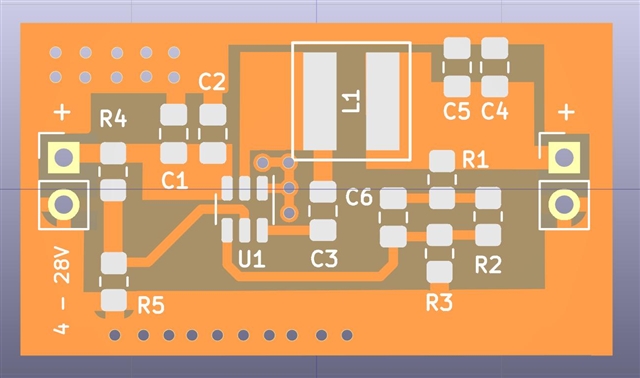

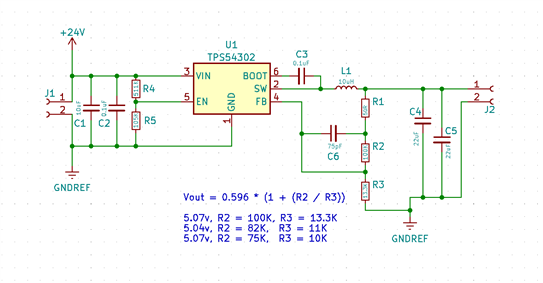

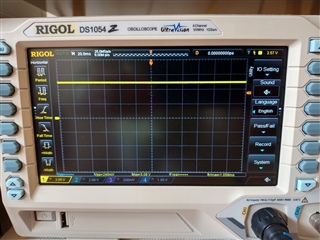

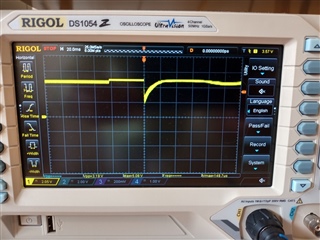

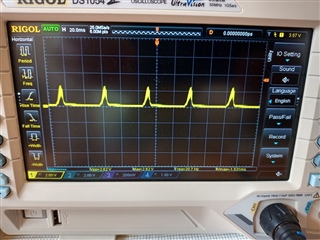

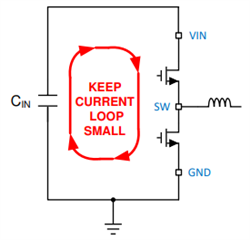

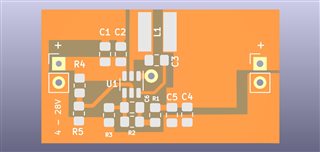

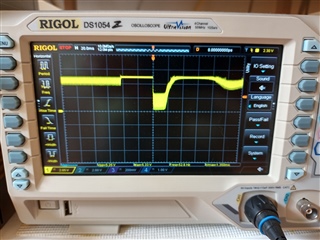

我想将 TPS54302DDCR 用于具有以下布局和组件的24V 至5V/500mA 降压电源。 负载大约为100mA 时、我似乎会出现输出电压干扰、其中电压在100us 后1-2V 下降、超过250mA IC 进入某种 PWM/关断模式、在这种模式下、我可以看到电压脉冲在500mV 到~2V 之间。 布局有什么问题吗? 谢谢

C1 = 10uF X7R

C2 = 0.1uF X7R

C3 =0.1uF X7R

C4 = 10 μ F X7R

C5 = 22uF X7R

C6 = 75pF X7R

R1 = 50R 1%

R2 = 75k 1%

R3 = 10K 1%

R4 = 510K 1%

R5 = 100k 1%

L1 = 10uH CDRH4D28NP-100NC