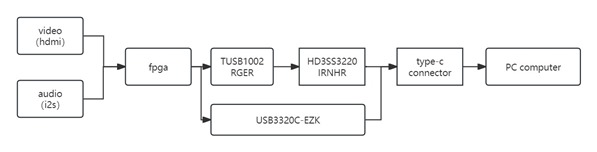

主题中讨论的其他器件:TUSB1064、 TUSB1002、TUSB1002A

您好!

我们使用了 TUSB1002RGER 和 HD3SS3220IRNHR。 当速度为5Gbps 时、USB 的两端都正常工作。 当速率为10Gbps 时、USB 只有一侧正常工作。

电路原理图已附。 您可以帮助检查是否存在电路问题吗?

e2e.ti.com/.../2783.schematic-diagram.pdf

我们还尝试了 TUSB1002RGER 和 VL160、两个 USB 端在5Gbps 和10Gbps 的速度下都运行良好;该项目用于通过 USB 将收集到的信息传输到计算机、应用是 UFP;

具有类似问题的帖子: HD3SS3220:HD3SS3220:只有 USB-C 的一侧正常工作、设计审查/调试-电源管理论坛-电源管理- TI E2E 支持论坛;

->文章讨论是 DFP,我不确定它是否适用于 UFP,例如:

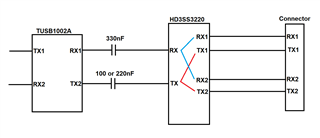

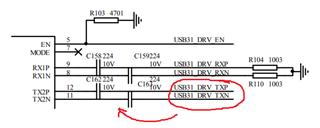

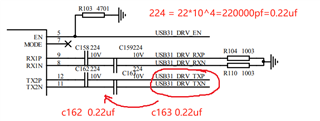

1. TUSB1002RGER 和 HD3SS3220IRNHR 之间是否需要耦合电容? 或直接直流耦合?

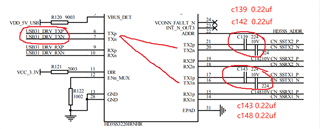

2. HD3SS3220IRNHR 的 RX1和 RX2是否需要耦合电容器?

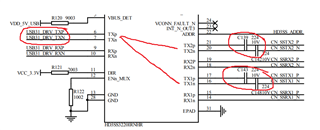

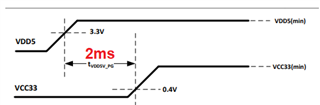

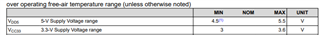

3.是否需要确保 VDD5引脚电压在 VCC33引脚上升之前保持稳定2ms? VCC33我们使用慢速上升而不是延迟上升。 慢速上升是否可行?

HD3SS3220IRNHR 的 VBUS_DET 引脚采用5V 电压连接、我是否需要控制 VBUS 的时序? 它现在失控了。

5.我们没有使用3.3V 电压、而是使用3.0V 电压。 这有影响吗?